# Individual Learning Program

# **MICROPROCESSORS**

Appendix B

DATA SHEETS

EE-3401

Courtesy of Motorola Semiconductor Products, Inc

# **CONTENTS**

| MC6800 Data Sheet          | . Page B-3 |

|----------------------------|------------|

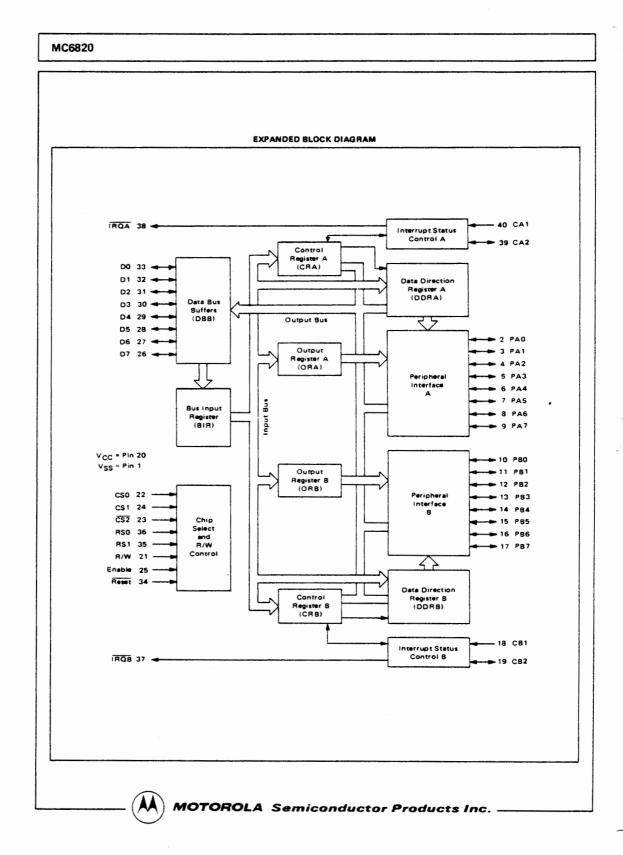

| MC6820 Data Sheet          | Page B-21  |

| MC6850 Data Sheet          | Page B-31  |

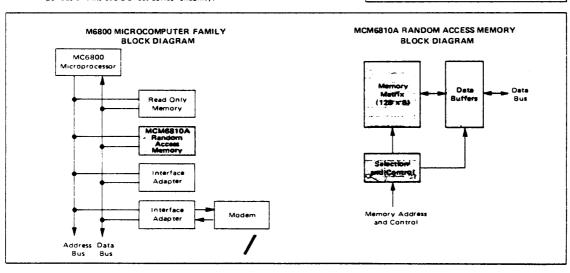

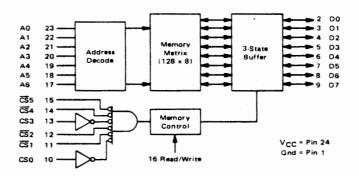

| MCM6810A Data Sheet        | Page B-39  |

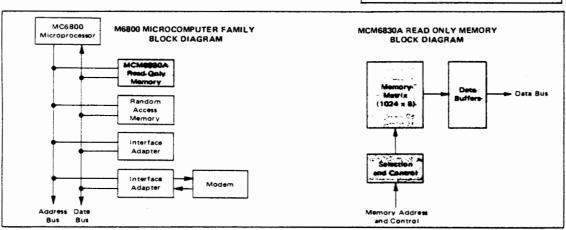

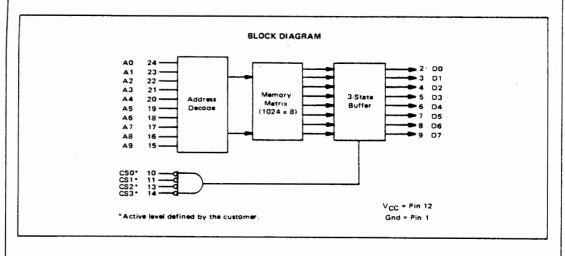

| MCM6830A Data Sheet        | Page B-43  |

| MCM6832 Data Sheet         | Page B-47  |

| Positive Powers of two     | Page B-51  |

| Negative Powers of two     | Page B-52  |

| Positive Powers of eight   | Page B-53  |

| Positive Powers of sixteen | Page B-53  |

| Negative Powers of sixteen | Page R-53  |

# **Advance Information**

# MICROPROCESSOR WITH CLOCK

The MC6808 is a monolithic 8-bit microprocessor that contains all the registers and accumulators of the present MC6800 plus an internal clock oscillator and driver on the same chip.

The MC6808 is completely software-compatible with the MC6800 as well as the entire M6800 family of parts. Hence the MC6808 is expandable to 65K words.

This very cost-effective MPU allows the designer to use the MC6808 in consumer as well as industrial applications without sacrificing industrial specifications.

- · On-Chip Clock Circuit

- Software-Compatible with the MC6800

- Expandable to 65K words

- Standard TTL-Compatible Inputs and Outputs

- 8-Bit Word Size

- 16-Bit Memory Addressing

- Interrupt Capability

# MOS

(N-CHANNEL, SILICON-GATE, DEPLETION LOAD)

**MICROPROCESSOR** WITH CLOCK

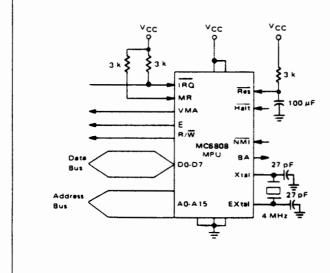

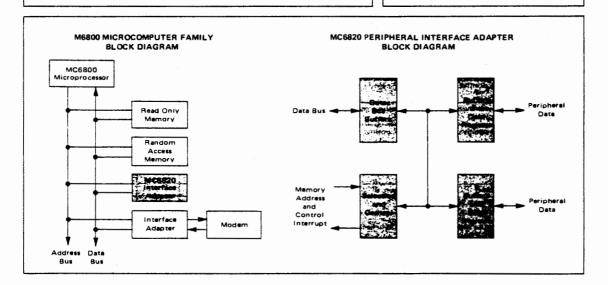

#### FIGURE 1 - TYPICAL MICROPROCESSOR INTERFACE

This is advance information and specifications are subject to change without notice.

CMOTOROLA INC 1978

AD1-805

|  |  | - | _ |

|--|--|---|---|

|  |  |   |   |

|  |  | _ | - |

|  |  |   |   |

|  |  |   |   |

|  |  |   |   |

|  |  |   | - |

|  |  |   | _ |

|  |  |   |   |

|  |  | _ | - |

|  |  |   |   |

|  |  | _ | - |

|  |  |   |   |

|  |  | _ | - |

|  |  | _ | _ |

|  |  |   |   |

|  |  | , | ~ |

|  |  |   |   |

|  |  | _ | - |

|  |  |   |   |

|  |  |   | - |

|  |  |   |   |

|  |  |   | - |

|  |  |   | _ |

|  |  |   |   |

|  |  | _ | - |

|  |  |   |   |

|  |  | _ | - |

|  |  |   |   |

|  |  | _ |   |

|  |  | ~ |   |

|  |  |   |   |

|  |  |   |   |

|  |  |   |   |

|  |  |   |   |

(0 to 70°C: L or P Suffi

# MC6800C

(-40 to 85°C; L Suffix only)

# MICROPROCESSING UNIT (MPU)

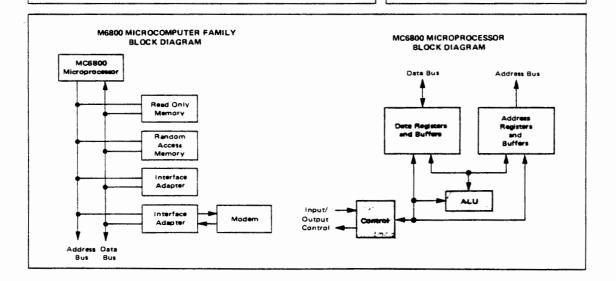

The MC6800 is a monolithic 8-bit microprocessor forming the central control function for Motorola's M6800 family. Compatible with TTL, the MC6800, as with all M6800 system parts, requires only one +5.0-volt power supply, and no external TTL devices for bus interface.

The MC6800 is capable of addressing 65K bytes of memory with its 16-bit address lines. The 8-bit data bus is bidirectional as well as 3-state, making direct memory addressing and multiprocessing applications realizable.

- · Eight-Bit Parallel Processing

- Bi-Directional Data Bus

- Sixteen-Bit Address Bus 65K Bytes of Addressing

- 72 Instructions Variable Length

- Seven Addressing Modes Direct, Relative, Immediate, Indexed, Extended, Implied and Accumulator

- Variable Length Stack

- Vectored Restart

- Maskable Interrupt Vector

- Separate Non-Maskable Interrupt Internal Registers Saved In Stack

- Six Internal Registers Two Accumulators, Index Register, Program Counter, Stack Pointer and Condition Code Register

- Direct Memory Addressing (DMA) and Multiple Processor Capability

- Clock Rates as High as 1 MHz

- Simple Bus Interface Without TTL

- Halt and Single Instruction Execution Capability

# MOS

(N-CHANNEL, SILICON-GATE)

MICROPROCESSOR

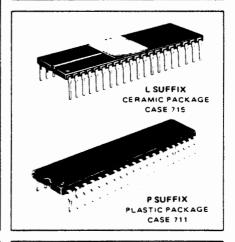

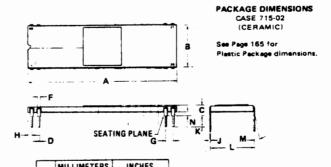

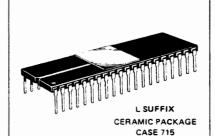

L SUFFIX CERAMIC PACKAGE CASE 715

NOT SHOWN: P SUFFIX

PLASTIC PACKAGE

CASE 711

| Characteristic                                            |                | Symbol           | Min                   | Тур   | Max                   | Unit |

|-----------------------------------------------------------|----------------|------------------|-----------------------|-------|-----------------------|------|

| Input High Voltage                                        | Logic          | VIH              | V <sub>SS</sub> + 2.0 | _     | V <sub>CC</sub>       | Vdc  |

|                                                           | φ1,φ2          | VIHC             | VCC - 0.3             | -     | VCC + 0.1             |      |

| Input Low Voltage                                         | Logic          | VIL              | V <sub>SS</sub> - 0.3 | -     | V <sub>SS</sub> + 0.8 | Vdc  |

|                                                           | φ1, <b>φ2</b>  | VILC             | VSS - 0.1             | -     | V <sub>SS</sub> + 0.3 |      |

| Clock Overshoot/Undershoot - Input High                   | Level          | Vos              | V <sub>CC</sub> - 0.5 | -     | V <sub>CC</sub> + 0.5 | Vdc  |

| - Input Low                                               | Level          |                  | VSS - 0.5             | -     | V <sub>SS</sub> + 0.5 |      |

| Input Leakage Current                                     |                | lin              |                       |       |                       | µAdc |

| (Vin = 0 to 5.25 V, VCC = max)                            | Logic *        |                  | -                     | 1.0   | 2.5                   |      |

| (V <sub>in</sub> = 0 to 5.25 V, V <sub>CC</sub> = 0.0 V)  | <b>⊘1, ⊘2</b>  |                  | -                     | -     | 100                   |      |

| Three-State (Off State) Input Current                     | D0-D7          | <sup>1</sup> TSI |                       | 2.0   | 10                    | μAdc |

| $(V_{in} 0.4 to 2.4 V, V_{CC} = max)$                     | A0-A15,R/W     |                  | -                     | -     | 100                   |      |

| Output High Voltage                                       |                | VOH              | 1                     |       | 1                     | Vdc  |

| (ILoad = -205 #Adc, VCC = min)                            | D <b>0</b> -D7 |                  | V <sub>SS</sub> + 2.4 | -     | - 1                   |      |

| (ILoad = -145 #Adc, VCC = min)                            | A0-A15,R/W,VMA |                  | V <sub>SS</sub> + 2.4 | -     | -                     |      |

| $(I_{Load} = -100  \mu Adc, V_{CC} = min)$                | BA             |                  | Vss + 2.4             | -     | -                     |      |

| Output Low Voltage                                        |                | VOL              | -                     | _     | V <sub>SS</sub> + 0.4 | Vdc  |

| (I Load = 1.6 mAde, VCC = min)                            |                | 1                |                       |       | 1 1                   |      |

| Power Dissipation                                         |                | PD               | -                     | 0.600 | 1.2                   | W    |

| Capacitance =                                             | φ1,φ2          | Cin              | 80                    | 120   | 160                   | pF   |

| (V <sub>in</sub> = 0, T <sub>A</sub> = 25°C, f = 1.0 MHz) | TSC            |                  | - 1                   |       | 15                    |      |

| ,                                                         | DBE            |                  | -                     | 7.0   | 10                    |      |

|                                                           | D <b>0</b> -D7 |                  | -                     | 10    | 12.5                  |      |

|                                                           | Logic Inputs   |                  | -                     | 6.5   | 8.5                   |      |

|                                                           | A0-A15,R/W,VMA | Cout             | -                     | -     | 12                    | рF   |

| Frequency of Operation                                    |                | f                | 0.1                   | _     | 1.0                   | MHz  |

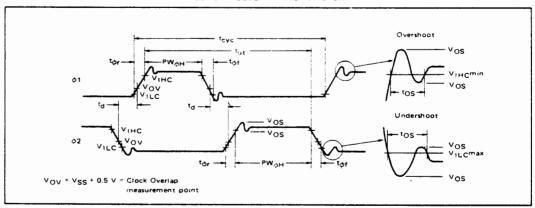

| Clock Timing (Figure 1)                                   |                |                  |                       |       |                       |      |

| Cycle Time                                                |                | tcyc             | 1.0                   | -     | 10                    | μs   |

| Clock Pulse Width                                         |                | PWoH             | 1                     |       | <b>†</b>              | ns   |

| (Measured at Voc - 0.3 V)                                 | 41             | 1                | 430                   | _     | 4500                  |      |

φ1 φ2

(Measured between  $V_{SS}$  + 0.3 V and  $V_{CC}$  - 0.3 V)

(Measured at  $V_{CC} = 0.3 \text{ V}$ )

Delay Time or Clock Separation

(Measured at  $V_{OV} = V_{SS} + 0.5 V$ )

Total \$1 and \$2 Up Time

Rise and Fall Times

Overshoot Duration

FIGURE 1 - CLOCK TIMING WAVEFORM

430

450

940

5.0

0

0

---

tut

tor, tof

td

tos

4500

4500

---

50

9100

ns

ns

<sup>\*</sup>Except IRQ and NMI, which require 3 k $\Omega$  pullup load resistors for wire-OR capability at optimum operation.

<sup>\*</sup>Capacitances are periodically sampled rather than 100% tested.

# **MAXIMUM RATINGS**

| Rating                      | Symbol           | Value        | Unit |

|-----------------------------|------------------|--------------|------|

| Supply Voltage              | Vcc              | -0.3 to +7.0 | Vdc  |

| Input Voltage               | Vin              | -0.3 to +7.0 | Vdc  |

| Operating Temperature Range | TA               | 0 to +70     | °C   |

| Storage Temperature Range   | T <sub>stg</sub> | -55 to +150  | °c   |

| Thermal Resistance          | ALθ              | 70           | °C/W |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

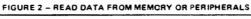

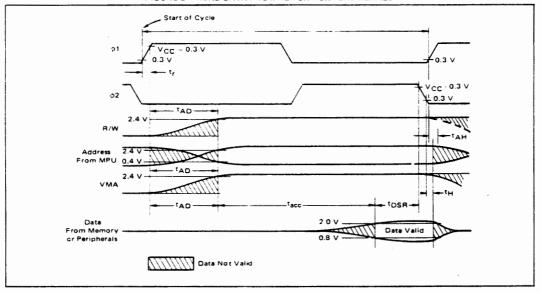

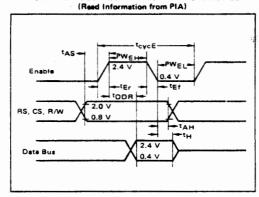

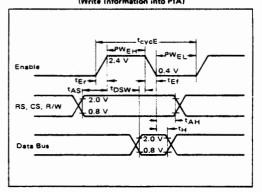

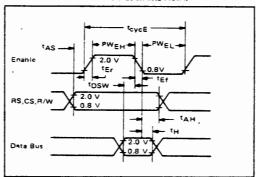

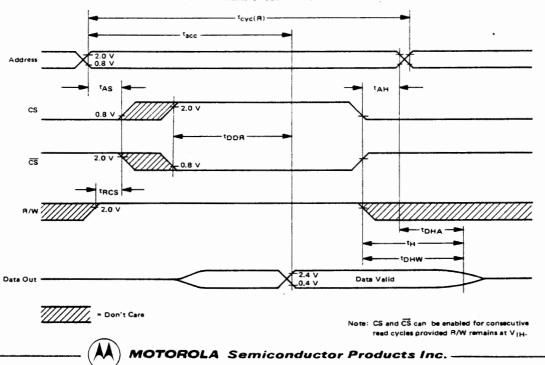

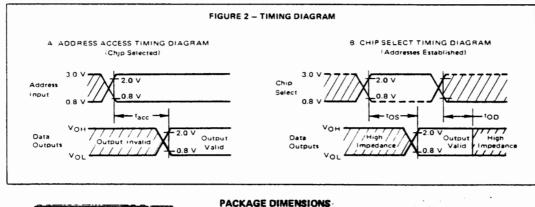

# READ/WRITE TIMING Figures 2 and 3, f = 1.0 MHz, Load Circuit of Figure 6.

| Characteristic                                         | Symbol           | Min | Тур | Max | Unit |

|--------------------------------------------------------|------------------|-----|-----|-----|------|

| Address Delay                                          | t <sub>AD</sub>  | _   | 220 | 300 | ns   |

| Peripheral Read Access Time  tacc = tut - (tAD + tDSR) | t <sub>acc</sub> | -   | -   | 540 | ns   |

| Data Setup Time (Read)                                 | <sup>†</sup> DSR | 100 | -   | -   | ns   |

| Input Data Hold Time                                   | tH               | 10  | -   | -   | ns   |

| Output Data Hold Time                                  | tH               | 10  | 25  | -   | ns   |

| Address Hold Time (Address, R/W, VMA)                  | t <sub>A</sub> H | 50  | 75  | -   | ns   |

| Enable High Time for DBE Input                         | t <sub>EH</sub>  | 450 | -   | -   | ns   |

| Data Delay Time (Write)                                | tDDW             | -   | 165 | 225 | ns   |

| Processor Controls*                                    |                  |     |     |     |      |

| Processor Control Setup Time                           | tPCS             | 200 | -   | - 1 | ns   |

| Processor Control Rise and Fall Time                   | tPCr. tPCf       | -   | -   | 100 | ns   |

| Bus Available Delay                                    | t <sub>BA</sub>  | -   | -   | 300 | ns   |

| Three State Enable                                     | tTSE             | -   | -   | 40  | ns   |

| Three State Delay                                      | tTSD             | -   | -   | 700 | ns   |

| Data Bus Enable Down Time During of Up Time (Figure 3) | †DBE             | 150 | _   | -   | ns   |

| Data Bus Enable Delay (Figure 3)                       | TOBED            | 300 | _   | -   | ns   |

| Data Bus Enable Rise and Fall Times (Figure 3)         | tDBEr, tDBEf     | -   | -   | 25  | ns   |

<sup>\*</sup>Additional information is given in Figures 12 through 16 of the Family Characteristics - see pages 17 through 20.

#### MPU SIGNAL DESCRIPTION

Proper operation of the MPU requires that certain control and timing signals be provided to accomplish specific functions and that other signal lines be monitored to determine the state of the processor.

Clocks Phase One and Phase Two  $(\phi 1, \phi 2)$  – Two pins are used for a two-phase non-overlapping clock that runs at the VCC voltage level.

Address Bus (A0-A15) — Sixteen pins are used for the address bus. The outputs are three-state bus drivers capable of driving one standard TTL load and 130 pF. When the output is turned off, it is essentially an open circuit. This permits the MPU to be used in DMA applications.

Data Bus (D0-D7) — Eight pins are used for the data bus. It is bi-directional, transferring data to and from the memory and peripheral devices. It also has three-state output buffers capable of driving one standard TTL load and 130 pF.

Halt — When this input is in the low state, all activity in the machine will be halted. This input is level sensitive. In the halt mode, the machine will stop at the end of an instruction, Bus Available will be at a one level, Valid Memory Address will be at a zero, and all other three-state lines will be in the three-state mode.

Transition of the Halt line must not occur during the last 250 ns of phase one. To insure single instruction operation, the Halt line must go high for one Clock cycle.

Three-State Control (TSC) — This input causes all of the address lines and the Read/Write line to go into the off or high impedance state. This state will occur 700 ns after TSC = 2.0 V. The Valid Memory Address and Bus Available signals will be forced low. The data bus is not affected by TSC and has its own enable (Data Bus Enable). In DMA applications, the Three-State Control line should be brought high on the leading edge of the Phase One Clock. The  $\phi1$  clock must be held in the high state and the  $\phi2$  in the low state for this function to operate properly. The address bus will then be available for other devices to directly address memory. Since the MPU is a dynamic device, it can be held in this state for only 4.5  $\mu s$  or destruction of data will occur in the MPU.

Read/Write (R/W) — This TTL compatible output signals the peripherals and memory devices whether the MPU is in a Read (high) or Write (low) state. The normal standby state of this signal is Read (high). Three-State Control going high will turn Read/Write to the off (high impedance) state. Also, when the processor is halted, it will be in the off state. This output is capable of driving one standard TTL load and 90 pF.

Valid Memory Address (VMA) — This output indicates to peripheral devices that there is a valid address on the address bus. In normal operation, this signal should be utilized for enabling peripheral interfaces such as the PIA and ACIA. This signal is not three-state. One standard TTL load and 90 pF may be directly driven by this active high signal.

Data Bus Enable (DBE) — This input is the three-state control signal for the MPU data bus and will enable the bus drivers when in the high state. This input is TTL compatible; however in normal operation, it would be driven by the phase two clock. During an MPU read cycle, the data bus drivers will be disabled internally. When it is desired that another device control the data bus such as in Direct Memory Access (DMA) applications, DBE should be held low.

Bus Available (BA) — The Bus Available signal will normally be in the low state; when activated, it will go to the high state indicating that the microprocessor has stopped and that the address bus is available. This will occur if the  $\overline{\text{Halt}}$  line is in the low state or the processor is in the WAIT state as a result of the execution of a WAIT instruction. At such time, all three-state output drivers will go to their off state and other outputs to their normally inactive level. The processor is removed from the WAIT state by the occurrence of a maskable (mask bit I=0) or nonmaskable interrupt. This output is capable of driving one standard TTL load and 30 pF.

Interrupt Request (IRQ) - This level sensitive input requests that an interrupt sequence be generated within the machine. The processor will wait until it completes the current instruction that is being executed before it recognizes the request. At that time, if the interrupt mask bit in the Condition Code Register is not set, the machine will begin an interrupt sequence. The Index Register, Program Counter, Accumulators, and Condition Code Register are stored away on the stack. Next the MPU will respond to the interrupt request by setting the interrupt mask bit high so that no further interrupts may occur. At the end of the cycle, a 16-bit address will be loaded that points to a vectoring address which is located in memory locations FFF8 and FFF9. An address loaded at these locations causes the MPU to branch to an interrupt routine in memory.

The Halt line must be in the high state for interrupts to be serviced. Interrupts will be latched internally while Halt is low.

The  $\overline{IRQ}$  has a high impadance pullup device internal to the chip; however a 3 k $\Omega$  external resistor to VCC should be used for wire-OR and optimum control of interrupts.

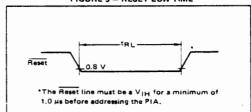

Reset — This input is used to reset and start the MPU from a power down condition, resulting from a power failure or an initial start-up of the processor. If a high level is detected on the input, this will signal the MPU to begin the restart sequence. This will start execution of a routine to initialize the processor from its reset condition. All the higher order address lines will be forced high. For the restart, the last two (FFFE, FFFF) locations in memory will be used to load the program that is addressed by the program counter. During the restart routine, the interrupt mask bit is set and must be reset before the MPU can be interrupted by IRQ.

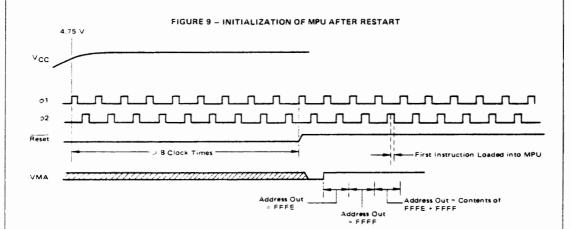

Figure 9 shows the initialization of the microprocessor after restart. Reset must be held low for at least eight clock periods after VCC reaches 4.75 volts. If Reset goes high prior to the leading edge of  $\phi$ 2, on the next  $\phi$ 1 the first restart memory vector address (FFFE) will appear on the address lines. This location should contain the higher order eight bits to be stored into the program counter. Following, the next address FFFF should contain the lower order eight bits to be stored into the program counter.

Non-Maskable Interrupt (NMI) — A low-going edge on this input requests that a non-mask-interrupt sequence be generated within the processor. As with the Interrupt Request signal, the processor will complete the current instruction that is being executed before it recognizes the NMI signal. The interrupt mask bit in the Condition Code Register has no effect on NMI.

The Index Register, Program Counter, Accumulators, and Condition Code Register are stored away on the stack. At the end of the cycle, a 16-bit address will be loaded that points to a vectoring address which is located in memory locations FFFC and FFFD. An address loaded at these locations causes the MPU to branch to a non-maskable interrupt routine in memory.

$\overline{NMI}$  has a high impedance pullup resistor internal to the chip; however a 3 k $\Omega$  external resistor to VCC should be used for wire-OR and optimum control of interrupts.

Inputs  $\overline{\text{IRQ}}$  and  $\overline{\text{NMI}}$  are hardware interrupt lines that are sampled during  $\phi 2$  and will start the interrupt routine on the  $\phi 1$  following the completion of an instruction.

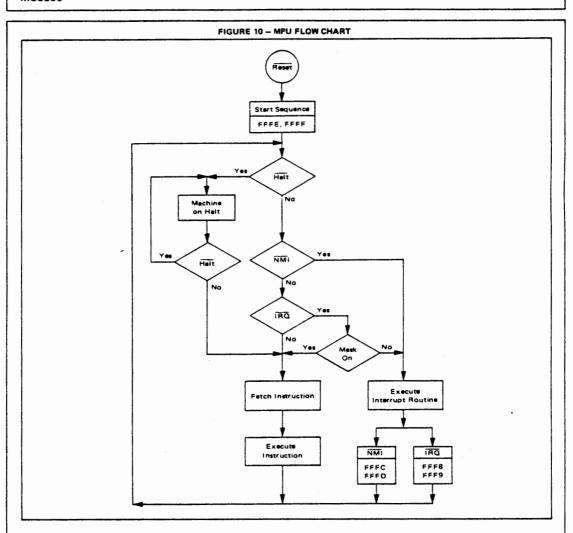

Figure 10 is a flow chart describing the major decision paths and interrupt vectors of the microprocessor. Table 1 gives the memory map for interrupt vectors.

TABLE 1 - MEMORY MAP FOR INTERRUPT VECTORS

| Vect | or   | Description            |

|------|------|------------------------|

| MS   | LS   | Description            |

| FFFE | FFFF | Restart                |

| FFFC | FFFD | Non-maskable Interrupt |

| FFFA | FFFB | Software Interrupt     |

| FFF8 | FFF9 | Interrupt Request      |

# MPU REGISTERS

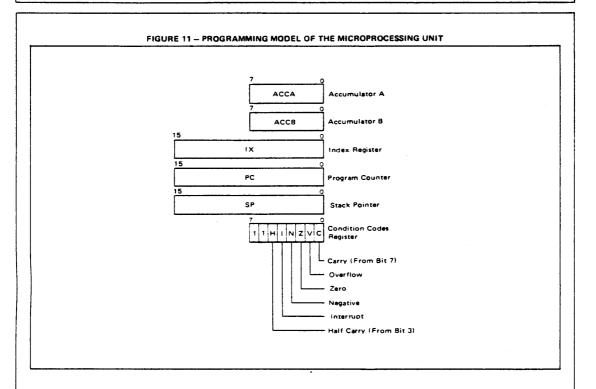

The MPU has three 16-bit registers and three 8-bit registers available for use by the programmer (Figure 11).

**Program Counter** – The program counter is a two byte (16-bits) register that points to the current program address.

Stack Pointer — The stack pointer is a two byte register that contains the address of the next available location in an external push-down/pop-up stack. This stack is normally a random access Read/Write memory that may

have any location (address) that is convenient. In those applications that require storage of information in the stack when power is lost, the stack must be non-volatile.

Index Register — The index register is a two byte register that is used to store data or a sixteen bit memory address for the Indexed mode of memory addressing.

Accumulators — The MPU contains two 8-bit accumulators that are used to hold operands and results from an arithmetic logic unit (ALU).

A

Condition Code Register - The condition code register indicates the results of an Arithmetic Logic Unit operation: Negative (N), Zero (Z), Overflow (V), Carry from bit 7 (C), and half carry from bit 3 (H). These bits of the Condition Code Register are used as testable conditions for the conditional branch instructions. Bit 4 is the interrupt mask bit (1). The unused bits of the Condition Code Register (b6 and b7) are ones.

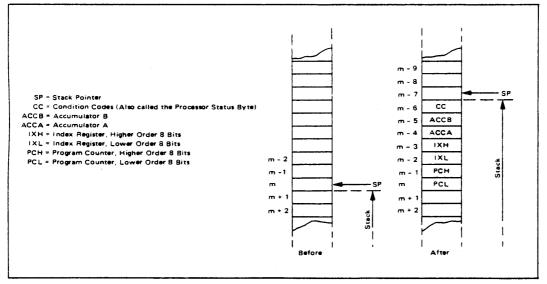

Figure 12 shows the order of saving the microprocessor status within the stack.

#### MPU INSTRUCTION SET

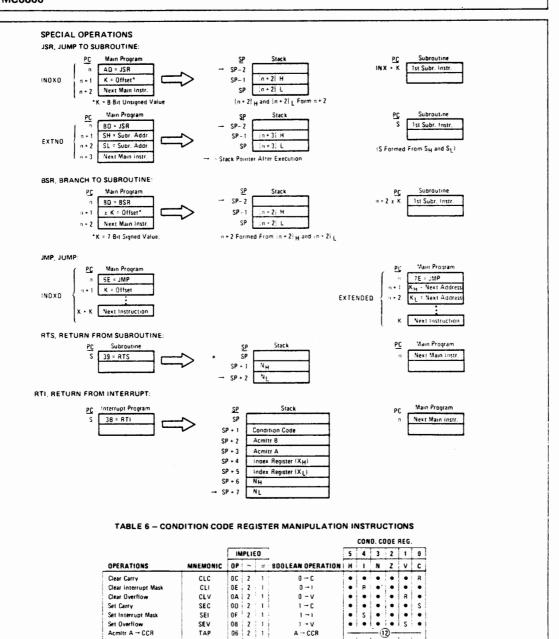

The MC6800 has a set of 72 different instructions. Included are binary and decimal arithmetic, logical, shift, rotate, load, store, conditional or unconditional branch, interrupt and stack manipulation instructions (Tables 2 thru 6).

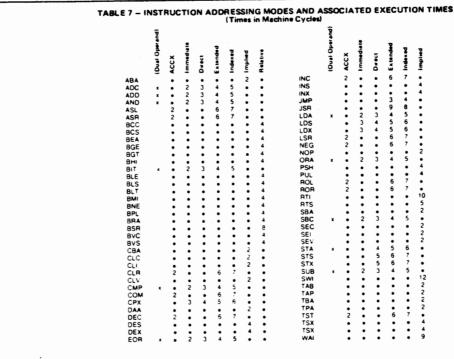

# MPU ADDRESSING MODES

The MC6800 eight-bit microprocessing unit has seven address modes that can be used by a programmer, with the addressing mode a function of both the type of instruction and the coding within the instruction. A summary of the addressing modes for a particular instruction can be found in Table 7 along with the associated instruction execution time that is given in machine cycles. With a clock frequency of 1 MHz, these times would be microseconds.

Accumulator (ACCX) Addressing - In accumulator only addressing, either accumulator A or accumulator B is specified. These are one-byte instructions.

Immediate Addressing - In immediate addressing, the operand is contained in the second byte of the instruction except LDS and LDX which have the operand in the second and third bytes of the instruction. The MPU addresses this location when it fetches the immediate instruction for execution. These are two or three-byte instructions.

Direct Addressing - In direct addressing, the address of the operand is contained in the second byte of the instruction. Direct addressing allows the user to directly address the lowest 256 bytes in the machine i.e., locations zero through 255. Enhanced execution times are achieved by storing data in these locations. In most configurations, it should be a random access memory. These are two-byte instructions.

Extended Addressing - In extended addressing, the address contained in the second byte of the instruction is used as the higher eight-bits of the address of the operand. The third byte of the instruction is used as the lower eight-bits of the address for the operand. This is an absolute address in memory. These are three-byte instructions.

Indexed Addressing - In indexed addressing, the address contained in the second byte of the instruction is added to the index register's lowest eight bits in the MPU. The carry is then added to the higher order eight bits of the index register. This result is then used to address memory. The modified address is held in a temporary address register so there is no change to the index register. These are two-byte instructions.

Implied Addressing - In the implied addressing mode the instruction gives the address (i.e., stack pointer, index register, etc.). These are one-byte instructions.

Relative Addressing - In relative addressing, the address contained in the second byte of the instruction is added to the program counter's lowest eight bits plus two. The carry or borrow is then added to the high eight bits. This allows the user to address data within a range of -125 to +129 bytes of the present instruction. These are twobyte instructions.

TABLE 2 - MICROPROCESSOR INSTRUCTION SET - ALPHABETIC SEQUENCE

| ABA                             | Add Accumulators                                                                       | CLR                      | Clear                                                                                | PUL                             | Pull Data                                                                                                                    |

|---------------------------------|----------------------------------------------------------------------------------------|--------------------------|--------------------------------------------------------------------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| ADC<br>ADD<br>AND<br>ASL<br>ASR | Add with Carry Add Logical And Arithmetic Shift Left Arithmetic Shift Right            | CLV<br>CMP<br>COM<br>CPX | Clear Overflow Compare Complement Compare Index Register                             | ROL<br>ROR<br>RTI<br>RTS        | Rotate Left<br>Rotate Right<br>Return from Interrupt<br>Return from Subroutine                                               |

| BCC<br>BCS<br>BEQ<br>BGE        | Branch if Carry Clear<br>Branch if Carry Set<br>Branch if Equal to Zero                | DAA<br>DEC<br>DES<br>DEX | Decimal Adjust Decrement Decrement Stack Pointer Decrement Index Register            | SBA<br>SBC<br>SEC<br>SEI        | Subtract Accumulators<br>Subtract with Carry<br>Set Carry<br>Set Interrupt Mask                                              |

| BGT                             | Branch if Greater or Equal Zero<br>Branch if Greater than Zero                         | EOR                      | Exclusive OR                                                                         | SEV                             | Set Overflow                                                                                                                 |

| BHI<br>BIT<br>BLE<br>BLS        | Branch if Higher<br>Bit Test<br>Branch if Less or Equal<br>Branch if Lower or Same     | INC<br>INS<br>INX<br>JMP | Increment Increment Stack Pointer Increment Index Register Jump                      | STA<br>STS<br>STX<br>SUB<br>SWI | Store Accumulator Store Stack Register Store Index Register Subtract Software Interrupt                                      |

| BLT<br>BMI                      | Branch if Less than Zero<br>Branch if Minus                                            | JSR                      | Jump to Subroutine                                                                   | TAB                             | Transfer Accumulators                                                                                                        |

| BNE<br>BPL<br>BRA<br>BSR        | Branch if Not Equal to Zero<br>Branch if Plus<br>Branch Always<br>Branch to Subroutine | LDA<br>LDS<br>LDX<br>LSR | Load Accumulator<br>Load Stack Pointer<br>Load Index Register<br>Logical Shift Right | TAP<br>TBA<br>TPA<br>TST        | Transfer Accumulators to Condition Code Reg.<br>Transfer Accumulators<br>Transfer Condition Code Reg. to Accumulator<br>Test |

| BVC<br>BVS                      | Branch if Overflow Clear<br>Branch if Overflow Set                                     | NEG<br>NOP               | Negate<br>No Operation                                                               | TSX                             | Transfer Stack Pointer to Index Register<br>Transfer Index Register to Stack Pointer                                         |

| CBA                             | Compare Accumulators Clear Carry                                                       | ORA                      | Inclusive OR Accumulator                                                             | WAI                             | Wait for Interrupt                                                                                                           |

| CLI                             | Clear Interrupt Mask                                                                   | PSH                      | Push Data                                                                            |                                 |                                                                                                                              |

|                     |              |          |     |     | ADDRESSING MODES |        |     |                     |   | BOOLEAN/ARITHMETIC OPERATION CONO. CODE REG. |          |   |     |     |   |    |                                            |       |   |       |       |                     |

|---------------------|--------------|----------|-----|-----|------------------|--------|-----|---------------------|---|----------------------------------------------|----------|---|-----|-----|---|----|--------------------------------------------|-------|---|-------|-------|---------------------|

|                     |              | 1        | MME | 0   | Ð                | REC    | T   | INDEX EXTND IMPLIED |   | : All register labels                        |          |   |     |     | 0 |    |                                            |       |   |       |       |                     |

| PERATIONS           | MNEMONIC     | OP       |     |     | OP               | ٠.     | = } | OP.                 |   | 2                                            | QP.      | _ | - 7 | OP  | - | =  | refer to contents)                         | H     | Т | N     | z [v  | C                   |

| dd                  | ADDA         | 38       | 2   | 2   | 38               | 3      | 2   | AB                  | 5 | 2                                            | 88       | 1 | 3   |     |   |    | A • 11 · A                                 | 1:    | • | : ;   | : [:  | 1:                  |

|                     | 40D8         | CB       | 2   | 2   | 08               | 3      | 2   | €B                  | 5 | 2                                            | FB       | 1 | 3   |     |   |    | 3 · M · 6                                  | 1:    | • | : [   |       |                     |

| ld Acmirs           | ABA          |          |     |     |                  | _      | . ! |                     |   | _                                            |          |   |     | 18  | 2 | 1  | A - 8 - A                                  |       | • |       |       |                     |

| d with Carry        | ADCA         | 39<br>59 | 2   | 2   | 39               | 3      | 2 ! |                     | 5 | 2                                            | B9       | 4 | 3   |     |   |    | 'A+M+C -A<br>'8+M+C -8                     | 133   | • | 1     |       | 1:                  |

| d                   | ADCE         | 34       | 2   | 2   | 94<br>94         | 3      | 2   | E9                  | 5 | 2                                            | F9<br>B4 | 1 | 3   |     |   |    |                                            |       | • | : :   |       | 1:                  |

| 1                   | 4006         | (4       | 2   | 2   | الهار<br>الهار   | j<br>J | 2   | E4                  | 5 | 2                                            | F4       |   | 3   |     |   |    | 8 · M · S                                  | :     |   | 11    | :   P |                     |

| Text                | RITA         | 35       | 2   | 2   | 35               | 3      | 2   | A5                  | 5 | 2                                            | 85       | 1 | 3   |     |   |    | : A · M                                    |       |   | : !   |       |                     |

| 1-3-                | 8:18         | CS       | 2   | 2   | 25               | 3      | 2   | 25                  | 5 | 2                                            | F 5      |   | 3   |     |   |    | 8 11                                       |       |   | ::    |       | •                   |

| df.                 | CLB          |          |     | 1   |                  |        | ì   | óF                  | 7 | 2                                            | 16       | ŝ | 2   |     |   |    | 90 - 4                                     |       | • | R     |       | R                   |

|                     | CLRA         |          |     |     |                  |        | - 1 |                     |   |                                              |          |   |     | 1F  | 2 | :  | 10 - A                                     | •     |   | я:    |       | R                   |

|                     | CLAB         |          |     |     |                  |        |     |                     |   |                                              |          |   | - 1 | 5F  | 2 | 2  | 90 - B                                     |       | • | Βį    | S F   | R                   |

| : Itale             | UNPA         | 31       | ž   | 2   | 31               | 3      | 2 ; |                     | 2 | 2                                            | 18       | : | 1   |     |   |    | . A 11                                     | •     | • | : 1   | 1     |                     |

|                     | CMPB         | (1       | 2   | 2   | 01               | 3      | ?   | ΕI                  | 5 | 2                                            | FI       | 1 | ; i |     |   |    | 8 W                                        | •     | • | :     |       | 1:                  |

| ngare Armors        | 684          | ŀ        |     |     |                  |        | - ! |                     |   |                                              |          |   | -   | 11  | 2 | *  | A 3                                        | : •   | • | :     |       | : :                 |

| agement 13          | CUM          |          |     |     |                  |        |     | 63                  | 7 | 2                                            | /3       | 6 | 3   |     |   |    | M - M                                      | •     |   | - 1   | :   9 | S                   |

|                     | COMA         |          |     |     |                  |        | i   |                     |   |                                              |          |   |     | 13  | 2 | 1  | ā. · a                                     | •     | • | . 1   |       | s                   |

|                     | COMB         |          |     |     |                  |        |     |                     |   |                                              |          |   |     | 23  | 2 | 1  | 8 -3                                       | •     | • | 1     |       | S                   |

| motement 2          | NEGA<br>NEGA |          |     |     |                  |        | !   | 60                  |   | 2                                            | 10       | h | 3 ! | ÷0  | , | 1  | 99 V - V<br>90 A - A                       | •     | : | : 1   |       | 0                   |

| qate:               | NEGA         |          |     |     |                  |        |     |                     |   |                                              |          |   |     | 50  | 2 |    | : 00 д - д<br>- 00 в - В                   |       | : |       |       | 0                   |

| imai Athisti, A     | DAA          |          |     |     |                  |        |     |                     |   |                                              |          |   |     | 19  | 2 | 1  | Converts Binary Add of BCD Characters      |       |   |       | . (Q  | 99                  |

|                     | 0.00         |          |     |     |                  |        |     |                     |   |                                              |          |   |     | ' ' | - | ,  | into BCD Format                            |       | • | ٠,    | ٠.    | 4                   |

| remend              | JEC          |          |     |     |                  |        |     | ÷Α                  | , | ٠, ١                                         | /A       | ó | 3.  |     |   |    | M : M                                      |       |   | . !   | :     |                     |

|                     | DECA         |          |     |     |                  |        |     | ,,,                 |   | -                                            |          | , |     | 14  | 2 | 1  | A 1 - A                                    |       |   | :     |       |                     |

|                     | GECB         |          |     |     |                  |        |     |                     |   |                                              |          |   |     | 54  | 2 | 1  | 5 1 4                                      |       |   | : 1   |       |                     |

| ا ا ا سر<br>۱) ا    | FURA         | 38       | 2   | 2.1 | 38               | 3      | 2 . | 48                  | 5 | 2                                            | 38       | : | 3 ' |     | - |    | AGM : A                                    |       |   | : 1   |       |                     |

|                     | EORB         | 5.3      | 2   | 2   | 38               | 3      | 2   | £3                  | 5 | 2                                            | F8       | 1 | 3 i |     |   |    | 8 E M + B                                  |       |   | ÷     | : l a |                     |

| project f           | 186          |          |     |     |                  |        |     | 6C                  |   | 2 '                                          | 70       | ŝ | 3   |     |   |    | 9-1-7                                      |       | • | : 1   | : 15  |                     |

|                     | NCA          |          |     |     |                  |        |     |                     |   |                                              |          |   | į   | ; ( | 2 | :  | A = 1 · A                                  | . • i | • | : •   | 15    | •                   |

|                     | ACS.         |          |     |     |                  |        |     |                     |   |                                              |          |   |     | 50  | 2 | 3  | 4-1-8                                      | •     | • | ::    | : 85  | <i>i</i> • <i>i</i> |

| Acoto               | AAC.         | ₹6       | 2   | 3.  | 36               | ;      | 2   | 46                  | 5 | 2                                            | 36       | 1 | 3   |     |   |    | 35 - A                                     | •     | • | 1     |       | •                   |

|                     | LOAS         | U6       | ?   | 2   | 06               | )      | 2 : | 8.5                 | 5 | 2                                            | +6       | : | 3   |     |   |    | , M S                                      | •     | • | : 1   | : 9   | 1 - 1               |

| THE FROM SHE        | AAFU         | ⊰Δ       | 2   | 2   | 92               | 3      | 2 ; | AA                  | 5 | 2                                            | 5A       | 4 | 3   |     |   |    | A + M + A                                  | •     | • | 11    | :   я |                     |

|                     | CRAB         | CA       | 2   | 2   | DA               | 3      | 2   | ЕΑ                  | 5 | 2                                            | FA       | 1 | 3   |     |   |    | 3 * M · 8                                  | •     | • | : [   | :   A |                     |

| Data                | PSHA         |          |     |     |                  |        | į.  |                     |   |                                              |          |   | i   | 36  | 1 | 1  | A - MgP SP 1 + SP                          | •     | • | -:    |       | •                   |

| Duta                | PULA         |          |     |     |                  |        | - 1 |                     |   |                                              |          |   | - 1 | 37  | 4 | 1  | B - Mgp SP 1 - SP<br>SP - 1 - SP Mgp - A   | •     | • | • 1   |       | •                   |

| 0318                | PULB         |          |     |     |                  |        |     |                     |   |                                              |          |   | - 1 | 33  | 4 | i  | SP - 1 - SP MSP - A<br>SP - 1 - SP MSP - R |       |   | H     | -   - |                     |

| ile fett            | 101          | •        |     |     |                  |        |     | 59                  | 7 | 2                                            | 79       | 6 | 3   | 33  | • |    | 7)                                         |       |   | -1    |       | :                   |

|                     | ROLA         | ĺ        |     |     |                  |        |     | ,,                  |   | `                                            |          | • | ٠,  | 19  | 2 | ,  |                                            |       |   | 1     |       | 1:                  |

|                     | ROLE         |          |     | -   |                  |        |     |                     |   |                                              |          |   | 2   | 59  | , | 1  | A)                                         |       |   | 11    |       | 1:                  |

| ate Auglit          | 808          |          |     |     |                  |        |     | 66                  | 1 | 2                                            | 76       | 6 | .3: |     | - |    | vi                                         |       |   | 1     | 16    | 1:                  |

|                     | RURA         |          |     |     |                  |        |     |                     |   | -                                            |          |   |     | 16  | 2 | :  | A) -= - ================================   |       | • | 11    |       | 4                   |

|                     | RORE         |          |     |     |                  |        | - ! |                     |   |                                              |          |   |     | 56  | 2 | 1  | C -10                                      |       | • | : :   | : 6   | <b>†</b> :          |

| t Lete Arethogetic  | ÷SL          |          |     |     |                  |        |     | 68                  | i | 2                                            | 78       | 6 | 3   |     |   |    | v1 _                                       | •     | • | :     | 16    | 1:1                 |

|                     | ÷SLA :       |          |     |     |                  |        |     |                     |   |                                              |          |   |     | 19  | 2 | 1  | A) 0 - 1111111-0                           | •     | • |       | 1/8   |                     |

|                     | ÷2FB         |          |     |     |                  |        |     |                     |   |                                              |          |   |     | 58  | 2 | !  | 31 4 4.                                    | •     | • |       | 16    |                     |

| ti Right Anthonetic | ASR          |          |     |     |                  |        |     | 51                  | į | 2 !                                          | 77       | 6 | 5 : |     |   |    | " — -                                      | •     | • |       | 16    |                     |

|                     | 458A<br>4588 |          |     |     |                  |        |     |                     |   |                                              |          |   |     | 47  | 2 | 1  | A                                          | •     | • |       | (6    | 1:1                 |

| t Basht Luan.       | LSR          |          |     |     |                  |        | - 1 | 64                  | , |                                              | 7.3      |   | 4.1 | 57  | 2 | 1  | - 1                                        | •     |   |       |       | 1:                  |

| ander suge          | LSRA         |          |     |     |                  |        |     | 04                  | ' | 2                                            | . 1      | 6 | 3   | 14  | 2 | ı. | 4)                                         | •     |   | R :   |       | 1: (                |

|                     | LSRU         |          |     | 1   |                  |        |     |                     |   |                                              |          |   | ٠.  | 54  | 2 | 1  | A 0 - 1 50 - C                             | •     |   | R :   |       | 11                  |

| Acmin               | 5144         |          |     | ,   | 9.7              | 4      | 2 : | Al                  | c | 2                                            | 87       | 5 | 3   | 94  | Ł | 1  | A - M                                      | •     | • | R     | 6     |                     |

|                     | STAB         |          |     |     | 07               | 1      | 2   | E/                  | 6 | 2                                            | F /      | 5 | 3   |     |   |    | 8 · V                                      |       |   | : [   |       |                     |

| un f                | 5U6A         | 40       | 2   | 2   | 90               | ;      | 2   | A()                 | 5 | 2 1                                          | 80       | 1 | 3 : |     |   |    | A 11 - A                                   |       |   | :1    |       |                     |

|                     | SUBB         | 00       | 2   | 2   | 00               | ì      | 2   | EQ                  | 5 | 2                                            | FO       | 1 | 3.  |     |   |    | 8 7 8                                      |       |   | i     |       | 1::                 |

| ract Acoustrs       | 38A          |          |     |     |                  |        |     |                     |   |                                              |          |   |     | 10  | 2 | 1  | A 8 - A                                    |       |   | :1    |       |                     |

| s with Curry        | SBCA         | 32       | 2   | 2   | 32               | 3      | 2   | AZ                  | 5 | 2                                            | 82       | 1 | 3 ! |     |   |    | A M C -A                                   |       | • | : [   |       |                     |

|                     | 2808         | C2       | 2   | 2   | 92               | 3      | 2   | ٤2                  | 5 | 2                                            |          | 4 | 3   |     |   |    | 8 W C -8                                   |       | • | 1     |       | 1:1                 |

| nster Acristics     | TAB          |          |     | - 1 |                  |        |     |                     |   | - 5                                          |          |   |     | 16  | 2 | 1  | A - S                                      |       | • | :1    | R     | •                   |

|                     | TBA          |          |     |     |                  |        |     |                     |   |                                              |          |   |     | 17  | 2 | 1  | 8 · A                                      | •     |   | :     | R     |                     |

| Lero or Manus       | rst          |          |     |     |                  |        |     | бD                  |   | 2                                            | 10       | 6 | 3 : |     |   | i  | ₩ 50                                       | •     |   | :   : | R     |                     |

|                     | TSTA<br>BTZT |          |     |     |                  |        |     |                     |   |                                              |          |   |     | 4D  | 2 | 1  | A 90                                       |       | • | :   : | R     |                     |

|                     |              |          |     | - 1 |                  |        |     |                     |   |                                              |          |   |     | 5D  | 2 | 1  | 8 00                                       |       | • | :1:   | į R   | R                   |

# LEGENO

- Decention Code (Mexadecinal)

Number of MPU Cicles

Number of MPU Cicles

Number of Program Bytes,

Arithmetic Phils,

Arithmetic Phils,

Southard AND,

MSp. Contents of memory rocation donnted to be Stack Pointer.

- Bounan Immosive OR

Boorean Exchasive OR

Complement of M

Transfer Into:

O Bit Zero

Byte Zero

- Note: Accumulator addressing mode instructions are included in the column for IMPLIED addressing

#### CONDITION CODE SYMBOLS:

- H Half carry from bir 3

I Interrupt mask

N Negative issuin birs

Z Zero totyte:

U Overtow 25-pangkinness

C Carry from bir 7

R Reset Always

S Sct Always

Est And set if true created otherwise

Not Affected

# TABLE 4 - INDEX REGISTER AND STACK MANIPULATION INSTRUCTIONS

|                       |          | 11 | MME | D | 0  | IRE | T | 1  | NOE | X |     | XTN | 0 | 1N | PL1 | 0   |                                                | 5   | 4   | 3        | Z į | 1   |

|-----------------------|----------|----|-----|---|----|-----|---|----|-----|---|-----|-----|---|----|-----|-----|------------------------------------------------|-----|-----|----------|-----|-----|

| POINTER OPERATIONS    | MNEMONIC | OP | ~   | = | OP | ~   | = | OP | ~   | = | GP  | ~   | = | 0P | ~   | æ   | BOOLEAN/ARITHMETIC OPERATION                   | н   |     | -        |     |     |

| Compare Index Reg     | CPX      | 8C | 3   | 3 | 90 | 4   | 2 | AC | 6   | 2 | ВC  | 5   | 3 |    |     |     | XH - M, XL - (M + 1)                           | •   | •   | 0        | : K | 3   |

| Decrement Index Reg   | DEX      |    |     | ļ |    |     |   |    | 1   |   | i   | 1   |   | 09 | 4   | 1   | X - 1 → X                                      | •   | •   | •        | : ; | •   |

| Decrement Stack Potr  | DES      | İ  |     | 1 |    |     |   | į  | 1   | 1 |     |     |   | 34 | 4   | 1   | SP - 1 → SP                                    |     | •   | •        | •   | •   |

| ncrement Index Reg    | INX      | 1  |     | 1 |    | ì   |   | Ì  | 1   |   |     |     | 1 | 08 | 4   | 1   | X + 1 → X                                      | •   | •   | •        | :   | •   |

| ncrement Stack Potr   | INS      | l  |     |   | 1  |     | ļ | ļ  | !   |   | 1   | 1   |   | 31 | 4   | 1   | SP + 1 → SP                                    | - 1 | - 1 | •        |     | - 1 |

| Load Index Reg        | LOX      | CE | 3   | 3 | 0E | 4   | 2 | EE | 6   | 2 | FE  | 5   | 3 |    | i   |     | $M \rightarrow X_{H_*}(M+1) \rightarrow X_{L}$ | •   | •   | 31       | : ; | R   |

| Load Stack Potr       | LOS      | 8E | 3   | 3 | 9E | 4   | 2 | AE | 6   | 2 | BE  | 5   | 3 | 1  |     |     | M SPH, (M + 1) -+ SPL                          |     |     | <b>3</b> |     |     |

| Store Index Reg       | STX      | i  |     |   | DF | 5   | 2 | EF | 7   | 2 | FF  | 6   | 3 | į  |     |     | $X_{H} = M, X_{L} \rightarrow (M+1)$           | •   | •   | 9        | ::  | R   |

| Store Stack Potr      | STS      | 1  |     |   | 9F | 5   | 2 | AF | 7   | 2 | 8 F | 6   | 3 |    |     | 1   | SPH - M. SPL - (M + 1)                         | •   | •   | 9        | : ; | R   |

| ndx Reg - Stack Potr  | TXS      | i  |     |   | l  |     |   |    | 1   | i | į   |     |   | 35 | 4   | 1   | X - 1 → SP                                     | •   | ٠į  | •        | •   | •   |

| Stack Potr - Indx Reg | TSX      |    |     |   |    |     | 1 | 1  | 1   |   |     |     |   | 30 | 4   | : 1 | SP + 1 → X                                     | •   | •   | •        | •   | •   |

# TABLE 5 - JUMP AND BRANCH INSTRUCTIONS

|                          |          |      |     |     |            |     |   |     |     |   |    |      |     |                           |     | CO  | NO. | . CO | DE   | REG |    |

|--------------------------|----------|------|-----|-----|------------|-----|---|-----|-----|---|----|------|-----|---------------------------|-----|-----|-----|------|------|-----|----|

|                          |          | RE   | LAT | IVE |            | NDE | X |     | XTN | 0 | 39 | #LII | ED  |                           | 5   | T   | Ī   | 3    | 2    | 1   | 1  |

| OPERATIONS .             | MREMONIC | OP   | ~   | #   | 00         | -   | # | OP  | Γ~  | # | OP | ~    | #   | BRANCH TEST               | . Н |     | ıŢ  | N    | Z    | ٧   | I  |

| Branch Always            | BRA      | 20   | 4   | 2   |            |     |   |     | ĺ   |   |    | i    |     | None                      | •   | 10  | • i | •    | •    | •   | T  |

| Branch If Carry Clear    | BCC      | 24   | 4   | 2   | 1          |     | 1 | l   |     | i | 1  | 1    | i   | C = 0                     | •   | 1   | • 1 | •    | •    | •   | 1  |

| Branch If Carry Set      | BCS      | 25   | 4   | 2   | 1          | 1   | 1 |     | 1   |   |    | i    | i   | C = 1                     | •   | 1 6 | •   | •    | •    | •   | 1  |

| Branch If = Zero         | BEQ      | 27   | 4   | 2   | 1          |     | 1 | 1   |     | 1 |    | 1    |     | Z = 1                     | •   |     | •   | •    | •    | •   | 1  |

| Branch If ≥ Zero         | BGE      | 7 2C | 4   | 2   |            | i   |   |     | ŀ   | 1 | į  | 1    |     | N ⊕ V = 0                 | •   |     | •   | •    | •    | •   | 1  |

| Branch If > Zero         | BGT      | 2E   | 4   | 2   | 1          |     |   |     | i   | 1 | 1  |      |     | Z + (N + V) = 0           | •   | ٠,  | •   | • i  | •    | •   | ŀ  |

| Branch If Higher         | вні      | 22   | 4   | 2   | 1          |     |   |     |     |   |    | 1    |     | C + Z = 0                 | •   |     | •   | • į  | •    | •   | 1  |

| Branch II < Zero         | BL€      | 2 F  | 4   | 2   |            | 1   |   |     |     | l | ĺ  | 1    |     | Z + (N @ V) = 1           | •   | 1 6 | •   | • i  | •    | •   | į. |

| Branch If Lower Or Same  | BLS      | 23   | 4   | 2   | 1          | 1   |   |     | -   |   | i  | İ    | į l | C + Z = 1                 | •   | 1 . | •   | •    | •    | •   | ١, |

| Branch If < Zero         | BLT      | 20   | 4   | 2   | 1          | 1   |   |     |     | 1 |    |      |     | N ⊕ V = 1                 | •   | 1   | •   | •    | • [  | •   |    |

| Branch If Minus          | BMI      | 28   | 4   | 2   | ĺ          |     |   |     | 1   |   |    | 1    |     | N = 1                     | •   |     | •   | ٠i   | •    | •   |    |

| Branch If Not Equal Zero | BNE      | 26   | 4   | 2   | 1          | !   |   |     |     |   | i  |      | 1   | Z = 0                     | •   | 1 6 | ) i | •    | •    | •   | 1. |

| Branch If Overflow Clear | BVC      | 28   | 4   | 2   |            | 1   |   | l   | ļ   |   |    | ĺ    |     | V = 0                     | •   | 1.  | ٠į  | •    | •    | •   | 1  |

| Branch If Overflow Set   | 8VS      | 29   | 4   | 2   | 1          |     | 1 | 1   | İ   | 1 | }  |      | 1   | V = 1                     | •   |     | •   | •    | •    | •   |    |

| Branch if Plus           | BPL      | 2A   | 4   | 2   |            | 1   | 1 |     | ļ   |   | i  | i    |     | N = 0                     | •   |     | •   | •    | •    | •   | ŀ, |

| Branch To Subroutine     | BSR      | 80   | 8   | 2   |            | ĺ   |   |     | 1   | 1 |    | 1    |     | <b>)</b>                  | •   | 1 6 | •   | ٠į   | •    | •   | 1  |

| Jump                     | JMP      |      |     |     | 6 <b>E</b> | 4   | 2 | 7 E | 3   | 3 |    | 1    |     | See Special Operations    | •   |     | •   | •    | •    | •   |    |

| Jump To Subroutine       | JSR      | Ì    |     | l   | AD         | 8   | 2 | ВО  | 9   | 3 |    |      |     | <b>)</b>                  | •   |     | ·   | •    | •    | •   | 1  |

| No Operation             | NOP      |      |     |     |            |     |   | i   |     | į | 01 | 2    | 1   | Advances Prog. Cntr. Only | •   |     | •   | ٠i   | •    | •   | 1  |

| Return From Interrupt    | RTI      | 1    |     |     |            |     |   | į   |     |   | 38 | 10   | 1   |                           | -   | _   | _   | (1)  | i) - | _   | _  |

| Return From Subroutine   | RTS      |      |     |     | 1          | 1   |   |     |     |   | 39 | 5    | 1   | )                         | •   |     | •   | • [  | •    | •   | 1  |

| Softwere Interrupt       | SWI      |      |     |     |            | 1   |   |     |     |   | 3F | 12   | 1   | See Special Operations    | •   | 1 . | •   | •    | •    | •   | 1  |

| Weit for Interrupt *     | WAI      | l    |     | 1   |            |     |   |     |     | i | 3€ | 9    | ,   | ).                        |     | 10  | ÌŒ  | •    | •    | •   | 1  |

"WAI puts Address Bus, R.W., and Data Bus in the three-state made while VMA is held low.

#### CCR → Acmitr A TPA 07 CCR -A CONDITION CODE REGISTER NOTES: (But set if test is true and cleared otherwise)

A - CCR

·12)·

TAP

| 1 | (Bit V) | Test: Result = 10000000?                                                 | 7  | (Bit N) | Test: Sign bit of most significant (MS) byte = 1?                 |

|---|---------|--------------------------------------------------------------------------|----|---------|-------------------------------------------------------------------|

| 2 | (Bit C) | Test: Result = 00000000?                                                 | 8  | (Bit V) | Test: 2's complement overflow from subtraction of MS bytes?       |

| 3 | (Bit C) | Test: Decimal value of most significant BCD Character greater than nine? | 9  | (Bit N) | Test: Result less than zero? (Bit 15 = 1)                         |

|   |         | (Not cleared if previously set.)                                         | 10 | (All)   | Load Condition Code Register from Stack, (See Special Operations) |

| 4 | (Bit V) | Test: Operand = 10000000 prior to execution?                             | 11 | (Bit I) | Set when interrupt occurs. If previously set, a Non-Maskable      |

| 5 | (Bit V) | Test: Operand = 011111111 prior to execution?                            |    |         | Interrupt is required to exit the west state.                     |

| 6 | (Bit V) | Test: Set equal to result of N⊕C after shift has occurred.               | 12 | (AH)    | Set according to the contents of Accumulator A.                   |

|   |         |                                                                          |    |         |                                                                   |

Acmitr  $A \rightarrow CCR$

NOTE Interrupt time is 12 cycles from the end of the instruction being executed, except following a WAT instruction. Then it is 4 cycles

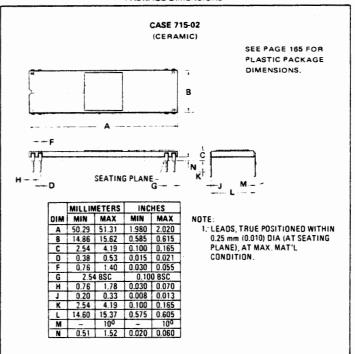

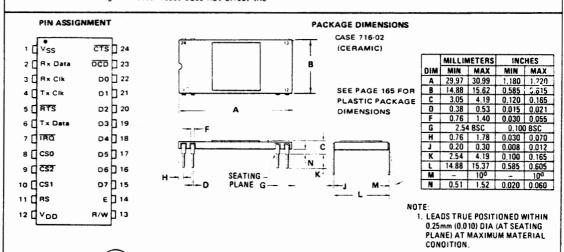

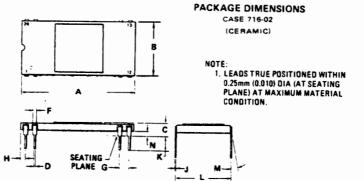

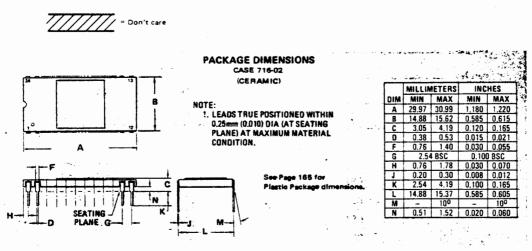

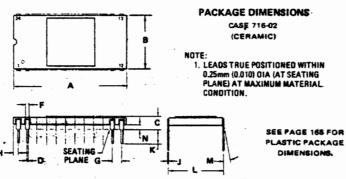

|     | MITTIE | EIENS | INC       | IES   |  |  |  |  |  |

|-----|--------|-------|-----------|-------|--|--|--|--|--|

| DIM | MIN    | MAX   | MIN       | MAX   |  |  |  |  |  |

| A   | 50.29  | 51.31 | 1.980     | 2.020 |  |  |  |  |  |

| В   | 14.86  | 15 62 | 0.585     | 0.615 |  |  |  |  |  |

| C   | 2.54   | 4.19  | 0.100     | 0.165 |  |  |  |  |  |

| 0   | 0.38   | 0.53  | 0.015     | 0.021 |  |  |  |  |  |

| F   | 0.76   | 1.40  | 0.030     | 0.055 |  |  |  |  |  |

| G   | 2.54   | BSC   | 0.100 BSC |       |  |  |  |  |  |

| Н   | 0.76   | 1.78  | 0.030     | 0.070 |  |  |  |  |  |

| J   | 0.20   | 0.33  | 0.008     |       |  |  |  |  |  |

| K   | 2.54   | 4.19  | 0.100     | 0.165 |  |  |  |  |  |

| Ļ   | 14.60  | 15.37 | 0.575     | 0.605 |  |  |  |  |  |

| M   | -      | 10°   | -         | 100   |  |  |  |  |  |

| N   | 0.51   | 1.52  | 0.020     | 0.060 |  |  |  |  |  |

11 E.

1. LEADS, TRUE POSITIONED WITHIN 0.25 mm (0.010) DIA (AT SEATING PLANE), AT MAX. MAT'L CONDITION.

# SUMMARY OF CYCLE BY CYCLE OPERATION

Table 8 provides a detailed description of the information present on the Address Bus, Data Bus, Valid Memory Address line (VMA), and the Read/Write line (R/W) during each cycle for each instruction.

This information is useful in comparing actual with expected results during debug of both software and hard-

ware as the control program is executed. The information is categorized in groups according to Addressing Mode and Number of Cycles per instruction. (In general, instructions with the same Addressing Mode and Number of Cycles execute in the same manner; exceptions are indicated in the table.)

#### TABLE 8 - OPERATION SUMMARY

| Address Mode and Instructions | Cycles   | Cycle | VMA<br>Line | Address Bus                             | R/W<br>Line | Deta Bus                        |

|-------------------------------|----------|-------|-------------|-----------------------------------------|-------------|---------------------------------|

| IMMEDIATE                     |          |       |             |                                         |             |                                 |

| ADC EOR                       |          | 1     | 1           | Op Code Address                         | 1           | Op Code                         |

| ADD LDA<br>AND ORA            | 2        | 2     | 1           | Op Code Address + 1                     | 1           | Operand Data                    |

| BIT SBC                       |          |       |             |                                         |             |                                 |

| CMP SUB                       | +        | 1     | 1           | Op Code Address                         | 1           | Op Code                         |

| LDS                           | 3        | 2     | ;           |                                         | 1           | Operand Data (High Order Byte)  |

| LDX                           | ,        | 3     | '           | Op Code Address + 1 Op Code Address + 2 |             | Operand Data (High Order Byte)  |

| DIRECT                        | L        |       |             | Op Code Address + 2                     | L.'.        | Operand Data (EDW Order Byte)   |

| ADC EOR                       | T        | 1     | 1 1         | Op Code Address                         | Ti          | Op Code                         |

| ADD LDA                       |          | 2     |             | Op Code Address + 1                     |             | Address of Operand              |

| AND ORA<br>BIT SBC            | 3        | 3     | 1           | Address of Operand                      | 1           | Operand Data                    |

| CMP SUB                       |          | ,     | '           | Address of Operand                      | '           | Operand Data                    |

| CPX                           |          | 1     | 1           | Op Code Address                         | 1           | Op Code                         |

| LDS<br>LDX                    | 4        | 2     | 1           | Op Code Address + 1                     | 1           | Address of Operand              |

|                               | -        | 3     | 1           | Address of Operand                      | 1 1         | Operand Data (High Order Byte)  |

|                               | 1        | 4     | 1           | Operand Address + 1                     | 1           | Operand Data (Low Order Byte)   |

| STA                           |          | 1     | 1           | Op Code Address                         | 1           | Op Code                         |

|                               | 4        | 2     | 1           | Op Code Address + 1                     | 1           | Destination Address             |

|                               |          | 3     | 0           | Destination Address                     | 1           | Irrelevant Data (Note 1)        |

|                               |          | 4     | 1           | Destination Address                     | 0           | Data from Accumulator           |

| STS                           |          | 1     | 1           | Op Code Address                         | 1           | Op Code                         |

| STX                           |          | 2     | 1           | Op Code Address + 1                     | 1           | Address of Operand              |

|                               | 5        | 3     | 0           | Address of Operand                      | 1           | Irrelevant Data (Note 1)        |

|                               |          | 4     | 1           | Address of Operand                      | 0           | Register Data (High Order Byte) |

|                               |          | 5     | 1           | Address of Operand + 1                  | 0           | Register Data (Low Order Byte)  |

| INDEXED                       |          |       |             |                                         |             |                                 |

| JMP                           |          | 1     | 1           | Op Code Address                         | 1           | Op Code                         |

|                               | 4        | 2     | 1           | Op Code Address + 1                     | 1 1         | Offset                          |

|                               |          | 3     | 0           | Index Register                          | 1 1         | Irrelevant Data (Note 1)        |

|                               | <u> </u> | 4     | 0           | Index Register Plus Offset (w/o Carry)  | 1           | Irrelevant Data (Note 1)        |

| ADC EOR<br>ADD LDA            |          | 1     | 1           | Op Code Address                         | 1           | Op Code                         |

| AND ORA                       | _        | 2     | 1           | Op Code Address + 1                     | 1           | Offset                          |

| BIT SBC<br>CMP SUB            | 5        | 3     | 0           | Index Register                          | 1           | Irrelevant Data (Note 1)        |

| CIMI 30B                      |          | 4     | 0           | Index Register Plus Offset (w/o Carry)  | 1 1         | Irrelevant Data (Note 1)        |

|                               |          | 5     | 1           | Index Register Plus Offset              | 1           | Operand Data                    |

| CPX<br>LDS                    |          | 1     | 1           | Op Code Address                         | 1 1         | Up Code                         |

| LDX                           |          | 2     | 1           | Op Code Address + 1                     | 1           | Offset                          |

|                               | 6        | 3     | 0           | Index Register                          | 1           | Irrelevant Data (Note 1)        |

|                               |          | 4     | 0           | Indax Register Plus Offset (w/o Carry)  | 1 1         | Irrelevant Data (Note 1)        |

|                               |          | 5     | 1           | Index Register Plus Offset              | 1           | Operand Data (High Order Byte)  |

|                               |          | 6     | 1           | Index Register Plus Offset + 1          | 1 1         | Operand Data (Low Order Byte)   |

| Address Mode        |        | Cycle        |          |                                         | R/W         | _                                                  |

|---------------------|--------|--------------|----------|-----------------------------------------|-------------|----------------------------------------------------|

| and Instructions    | Cycles | #            | Line     | Address Bus                             | Line        | Data Bus                                           |

| INDEXED (Continued) |        | 1            | 1        | Op Code Address                         | 1           | Op Code                                            |

| <b>3</b> 10         |        | 2            | ,        | Op Code Address + 1                     |             | Offset                                             |

|                     |        | 3            | 0        | Index Register                          | ;           | Irrelevant Data (Note 1)                           |

|                     | 6      | 4            | 0        | Index Register Plus Offset (w/o Carry)  | ;           |                                                    |

|                     |        | 5            | 0        | Index Register Plus Offset (W/O Carry)  | 1           | Irrelevant Data (Note 1) Irrelevant Data (Note 1)  |

|                     |        | 6            | 1        | Index Register Plus Offset              | ,           | Operand Data                                       |

| ASL LSR             |        | <del>-</del> | 1        | Op Code Address                         | 1           | Op Code                                            |

| ASR NEG             |        | 2            | 1        | Op Code Address + 1                     | ,           | Offset                                             |

| CLR ROL<br>COM ROR  |        | 3            | 0        | Index Register                          | 1           | irrelevant Data (Note 1)                           |

| DEC TST             | 7      | 4            | 0        | Index Register Plus Offset (w/o Carry)  | 1           | Irrelevant Data (Note 1)                           |

| INC                 |        | 5            | 1        | Index Register Plus Offset              | 1           | Current Operand Data                               |

|                     |        | 6            | 0        | Index Register Plus Offset              |             | Irrelavant Data (Note 1)                           |

|                     |        | 7            | 1/0      | Index Register Plus Offset              | ò           | New Operand Data (Note 3)                          |

|                     |        |              | (Note    |                                         | ŭ           | Trem Operano Data (Note 3)                         |

|                     |        |              | 3)       |                                         |             | 0-0-1                                              |

| STS<br>STX          |        | 1            | 1        | Op Code Address                         | 1           | Op Code                                            |

|                     |        | 2            | 1        | Op Code Address + 1                     | 1           | Offset                                             |

|                     | 7      | 3            | 0        | Index Register                          | 1           | Irrelevant Data (Note 1)                           |

|                     |        | 4            | 0        | Index Register Plus Offset (w/o Carry)  | 1           | Irrelevant Data (Note 1)                           |

|                     |        | 5            | 0        | Index Register Plus Offset              | 1           | Irrelevant Data (Note 1)                           |

|                     |        | 6            | 1        | Indax Register Plus Offset              | 0           | Operand Data (High Order Byte)                     |

|                     |        | 7            | 1        | Index Register Plus Offset + 1          | 0           | Operand Data (Low Order Byte)                      |

| JSR                 |        | 1            | 1        | Op Code Address                         | 1           | Op Code                                            |

|                     |        | 2            | 1        | Op Code Address + 1                     | 1           | Offset                                             |

|                     |        | 3            | 0        | Index Register                          | 1           | Irrelevant Data (Note 1)                           |

|                     | 8      | 4            | 1        | Stack Pointer                           | 0           | Return Address (Low Order Byta)                    |

|                     |        | 5            | 1        | Stack Pointer — 1                       | 0           | Return Address (High Order Syte)                   |

|                     |        | 6            | 0        | Stack Pointer — 2                       | 1           | Irrelevant Data (Note 1)                           |

|                     |        | 7            | 0        | Index Register                          | 1           | Irrelevant Data (Note 1)                           |

| EXTENDED            | 1      | 8            | 0        | Index Register Plus Offset (w/o Carry)  | 1           | Irrelevant Data (Note 1)                           |

| JMP                 |        | 1            | 1        | Op Code Address                         | 1           | 0-0-4                                              |

| ALVIP               | 3      | 2            | 1        | Op Code Address + 1                     | 1           | Op Code                                            |

|                     | 3      | 3            | 1        | Op Code Address + 2                     | 1           | Jump Address (High Order Byte)                     |

| ADC EOR             |        | 1            | 1        | Op Code Address + 2                     | <del></del> | Jump Address (Low Order Byte)                      |

| ADD LDA             |        | 2            | 1        |                                         | 1           | Op Code                                            |

| AND ORA             | 4      | 3            | 1        | Op Code Address + 1                     |             | Address of Operand (High Order Syte                |

| BIT SBC             |        | 4            | ' i      | Op Code Address + 2 Address of Operand  | 1           | Address of Operand (Low Order Byte                 |

| CPX                 |        | 1            | 1        |                                         |             | Operand Data                                       |

| DS                  |        | - 1          | 1        | Op Code Address                         | !           | Op Code                                            |

| LDX                 | 5      | 2            | 1        | Op Code Address + 1 Op Code Address + 2 | 1           | Address of Operand (High Order Byte                |

|                     | • •    | 4            | 1        |                                         | 1           | Address of Operand (Low Order Byte                 |

|                     | Ì      | 5            | ,        | Address of Operand                      | !           | Operand Data (High Order Byte)                     |

| STA A               |        | 1            | 1        | Address of Operand + 1                  |             | Operand Data (Low Order Byte)                      |

| TA B                | 1      |              |          | Op Code Address                         | 1           | Op Code                                            |

|                     | - 1    | 2            | !        | Op Code Address + 1                     | 1           | Destination Address (High Order Byte               |

| i                   | 5      | 3            | 1        | Op Code Address + 2                     | 1           | Destination Address (Low Order Byte                |

|                     |        | 4            | 0        | Operand Destination Address             | 1           | irrelevant Data (Note 1)                           |

| 120                 |        | 5            |          | Operand Destination Address             | 0           | Data from Accumulator                              |

| ASL LSR<br>ASR NEG  |        | 1            | 1        | Op Code Address                         | 1           | Op Code                                            |

| CLR ROL             |        | 2            | !        | Op Code Address + 1                     | !           | Address of Operand (High Order Byte                |

| COM ROR<br>DEC TST  | 6      | 3            | !        | Op Code Address + 2                     | 1           | Address of Operand (Low Order Byte)                |