# Individual Learning Program

### **MICROPROCESSORS**

### Unit 4 INTRODUCTION TO PROGRAMMING

EE-3401

HEATH COMPANY

BENTON HARBOR, MICHIGAN 49022

Copyright © 1977

Heath Company

All Rights Reserved

Printed in the United States of America

#### **CONTENTS**

| Introduction                 |

|------------------------------|

| Unit Objectives              |

| Unit Activity Guide 4-5      |

| Branching 4-6                |

| Conditional Branching 4-20   |

| Algorithms                   |

| Additional Instructions 4-46 |

| Experiments 4-58             |

| Unit Examination 4-59        |

| Examination Anaulana         |

## Unit 4 INTRODUCTION TO PROGRAMMING

#### **INTRODUCTION**

In the final analysis there are only two things you can do with a microprocessor. You can program it and you can interface it with the outside world. In this course, you learn to program the microprocessor first. This unit, along with the associated cassette tape and experiments, will serve as an introduction to programming.

The programs you encounter in this unit are simple enough that anyone can understand them, and yet they illustrate many important concepts. By studying these programs, you will develop an understanding of how the microprocessor handles complex tasks. At the same time, you will gain practice using the instruction set.

#### UNIT OBJECTIVES

When you have completed this unit, you will be able to:

- 1. Explain the difference between machine language, assembly language, interpretive language, and compiler language.

- 2. Define assembler, compiler, interpreter, object program, source program, BASIC, FORTRAN, and COBOL.

- 3. Draw the symbols used in flow charting and explain the purpose of each.

- 4. Develop flow charts that illustrate step-by-step procedures for solving simple problems.

- Explain the purpose of conditional and unconditional branching. 5.

- 6. Using the block diagram of the hypothetical microprocessor, trace the data flow during the execution of a branch instruction.

- 7. Compute the proper relative address for branching forward or backward from one point to another in a program.

- 8. Explain the purpose of the carry, negative, zero, and overflow flags. Give an example of a situation that can cause each to be set and another example that will cause each to clear. List eight instructions that test one of these flags.

- 9. Write programs that can: multiply by repeated addition; divide by repeated subtraction; convert binary to BCD; convert BCD to binary; add multiple-precision numbers; subtract multiple-precision numbers; add BCD numbers.

#### **UNIT ACTIVITY GUIDE**

|                                                                                                           | Time        |

|-----------------------------------------------------------------------------------------------------------|-------------|

| Play Cassette Tape Section "Introduction to Programming."                                                 |             |

| Read Section on Branching.                                                                                | <del></del> |

| <ul><li>Complete Self-Test Review Questions 1-9.</li><li>Read Section on Conditional Branching.</li></ul> |             |

| Complete Self-Test Review Questions 10-19.                                                                |             |

| Read Section on Algorithms.  Complete Self-Test Review Questions 20-29.                                   | ·           |

| Read Section on Additional Instructions.                                                                  |             |

| Complete Self-Test Review Questions 30-37.                                                                |             |

| Perform Programming Experiments 5 and 6.                                                                  |             |

| Complete Unit Examination.                                                                                | <del></del> |

| Check Examination Answers.                                                                                | <del></del> |

#### **BRANCHING**

The programs discussed earlier were all "straight line" programs: the instructions were executed one after another in the order in which they were written. Programs of this type are extremely limited because they use only a fraction of the microprocessor's power.

The real power of the microprocessor comes from its ability to execute a section of a program over and over again. In an earlier program we saw that two numbers could be multiplied by repeated addition. As long as the numbers are very small and we know the value of the two numbers, we can write a "straight line" program to multiply the numbers. For example, 9 could be multiplied by 4 with the following program:

| Address | Instruction/Data | Comments    |

|---------|------------------|-------------|

| 00      | LDA 05           | Load direct |

| 01      | ADD 05           | Add direct  |

| 02      | ADD 05           | Add direct  |

| 03      | ADD 05           | Add direct  |

| 04      | HLT              |             |

| 05      | 09               |             |

This technique is very crude for a number of reasons. If the two numbers are large, such as 98 and 112, the number of ADD instructions becomes excessive. Moreover, the values of the two numbers to be multiplied are generally not known. Therefore, even if we were willing to write enough ADD instructions, we simply would not know how many to write. Obviously, some better technique must be available.

A technique that is used in virtually every program is called **looping**. This allows a section of the program to be run as often as needed. Every microprocessor has a group of instructions called JUMP or BRANCH instructions that allow it to execute these program loops. These allow the microprocessor to escape the normal instruction sequence.

The microprocessor discussed in this course has both jump and branch instructions. In this unit, we will confine our discussion to the branch instructions. In a later unit we will discuss the jump instructions.

Before discussing the types of branch instructions, we must first discuss a new addressing mode called relative addressing.

#### **Relative Addressing**

In previous units, we discussed immediate addressing and direct addressing. Recall that in the immediate addressing mode no address is specified. The data is assumed to be the byte following the opcode. In direct addressing, an address is given. The data is assumed to be at that address.

Branch instructions are somewhat different from the instructions discussed earlier. While the branch instruction has an address associated with it, the address does not indicate the location of data. Instead, the address indicates the location of the next instruction that is to be executed.

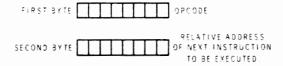

The format of the branch instruction is shown in Figure 4-1. All branch instructions are 2-byte instructions. The first byte is the 8-bit opcode. This code identifies the particular type of branch instruction. As you will see later, a microprocessor may have a dozen or more different branch instructions. Each has its own opcode that uniquely identifies it.

Figure 4-1 Format of the branch instruction.

The second byte of the branch instruction indicates the point to which the program is to branch. That is, it specifies the address of the next instruction that is to be executed.

In some microprocessors, the address is absolute. That is, the address is the memory location that holds the next instruction. In this case, the instruction BRANCH  $30_{16}$  would mean that the instruction to be executed next is at address  $30_{16}$ . In other words, some microprocessors use direct addressing when branching.

Our hypothetical microprocessor uses a different technique called relative addressing. In this addressing mode, the byte following the opcode does not represent an absolute address. Instead, it is a number that must be added to the program counter to form the new address. Consider the instruction:

Using relative addressing, this does not mean that the next instruction is to be taken from memory location  $30_{16}$ . Rather, it means that  $30_{16}$  must be added to the present contents of the program counter. Thus, if the program counter is at  $08_{16}$  when the BRANCH  $30_{16}$  instruction is executed, the next instruction will be fetched from location  $08_{16} + 30_{16} = 38_{16}$ .

By the same token, if the contents of the program counter is  $FA_{16}$  when a BRANCH 03 is encountered, the next instruction will be fetched from location  $FA_{16} + 03 = FD_{16}$ . Notice that this allows the MPU to jump over the instructions at addresses  $FB_{16}$  and  $FC_{16}$ .

#### **Executing a Branch Instruction**

Determining the relative address to use as the second byte of the branch instruction can be confusing unless you keep in mind the method by which the MPU executes a program. Therefore, let's go through the manipulations that take place within the MPU during the execution of the branch instruction.

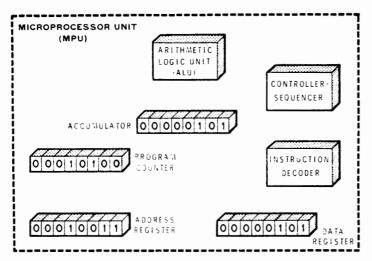

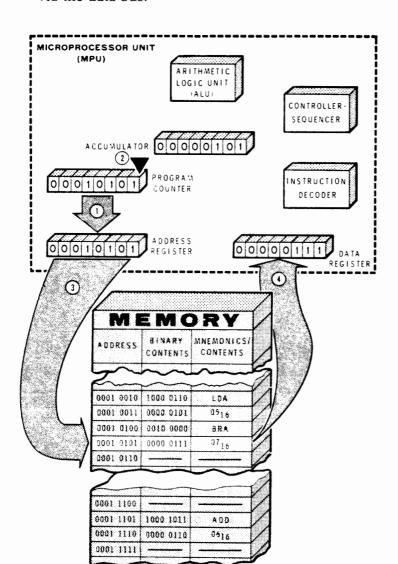

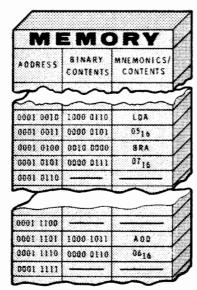

Figure 4-2 shows sections of a program stored in memory. Let's assume that the MPU has been executing this program. Let's further assume that the MPU just completed the execution of the LDA 05 instruction at addresses 12<sub>16</sub> and 13<sub>16</sub>. The address register still holds the address of the last byte that was read from memory. The accumulator and data register hold the contents (05) of the last location that was read out.

Notice that the program counter contains the address of the next instruction to be executed. This address points to the branch instruction in memory location 14<sub>16</sub>. Let's pick up the action at this point.

Figure 4-2

Status of the MPU registers after executing the LDA 05 instruction.

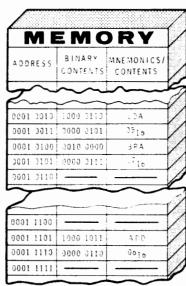

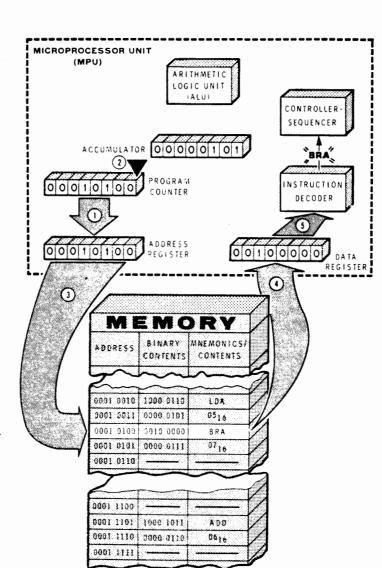

Figure 4-3 shows how the first byte of the branch instruction is fetched. This is the standard fetch operation that was discussed earlier:

- 1. The address  $(14_{16})$  is transferred from the program counter to the address register.

- 2. The program counter is incremented to 15<sub>16</sub>.

- 3. The address is strobed onto the address bus.

- 4. The contents of the selected memory location are transferred via the data bus to the data register.

- The instruction decoder examines this opcode and finds it to be a branch instruction.

Figure 4-3 Fetching the BRA instruction.

Therefore, the controller-sequencer starts the procedure for executing a branch instruction.

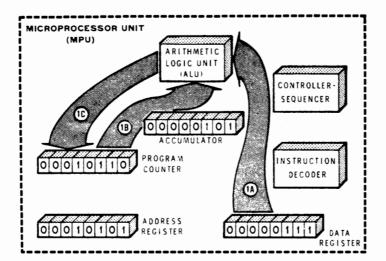

During the next machine cycle, the relative address is fetched. This procedure is shown in Figure 4-4. The major events are:

- 1. The address (15<sub>16</sub>) is transferred from the program counter to the address register.

- The program counter is incremented to 16<sub>16</sub>.

- 3. The address  $(15_{16})$  is strobed onto the address bus.

- 4. The contents of location  $15_{16}$  are transferred to the data register via the data bus.

Figure 4-4 Fetching the relative address.

Figure 4-5 shows the state of the various registers after the relative address is fetched. The relative address (07<sub>16</sub>) is in the data register. Now look at the program counter. Notice that it points to address 16<sub>16</sub>. However, the MPU has not yet finished executing the branch instruction. It must now compute the new address by adding the relative address to the program count. It uses the addition capabilities of the ALU to perform this function. That is, the program count and relative address are strobed into the ALU. The ALU adds the two together and produces a sum of

| 0001 | 0110 | program count     |  |  |

|------|------|-------------------|--|--|

| 0000 | 0111 | relative address  |  |  |

| 0001 | 1101 | new program count |  |  |

This sum is loaded into the program counter. Thus, the next instruction is fetched from memory location  $1D_{16}$ . That is, the next instruction to be executed is the ADD  $06_{16}$  instruction.

Figure 4-5

Computing the address of the next instruction.

A

#### **Branching Forward**

Branching in the forward direction is a simple task if you know the value of the program count when the relative address is added. A couple of examples will illustrate the procedure.

In Figure 4-6A, the BRANCH 03 instruction is placed in locations 32<sub>16</sub> and 33<sub>16</sub>. Assuming this instruction is executed, from which location will the next instruction be fetched? Remember that the program counter will always point to the next byte in sequence. Since the last byte fetched was the relative address from location 3316, the program counter must be at 34<sub>16</sub> when the relative address is added. Adding the relative address produces a new program count of

$$34_{16} + 3_{16} = 37_{16}$$

Thus, the next instruction will be fetched from location 37<sub>16</sub>.

| HEX                                    | HEX                          | MNEMONICS/                    |

|----------------------------------------|------------------------------|-------------------------------|

| ADDRESS                                | CONTENTS                     | HEX CONTENTS                  |

| 32<br>33<br>34<br>35<br>36<br>37<br>38 | 20<br>03<br>—<br>—<br>—<br>— | BRA<br>03<br>—<br>—<br>—<br>— |

Program will branch to here

Figure 4-6 Branching forward.

| HEX<br>ADDRESS | HEX<br>CONTENTS          | MNEMONICS/<br>HEX CONTENTS |   |

|----------------|--------------------------|----------------------------|---|

| 18             | 20                       | BRA                        |   |

| 19             | ??                       | ??                         | 1 |

| 1A ~           | 1                        | 1                          | 1 |

| 1B             | Originating Address      |                            | ı |

| 1C             |                          |                            | l |

| 1D             |                          | į                          | l |

| 1E             | 1                        | Ì                          | ı |

| 1F             |                          |                            | ı |

| 20             | 1                        |                            | ı |

| 21             |                          |                            | l |

| ( 22           | ]<br>Double of the first |                            | • |

| 23             | Destination Address      |                            | 1 |

| 24             |                          |                            | 1 |

| /              |                          | L                          | i |

We wish to Branch to here

Figure 4-6B shows a slightly different situation. Here we wish to branch to the instruction at address  $24_{16}$ . The opcode for the branch instruction is at address  $18_{16}$ . What relative address is required at location  $19_{16}$  in order to implement this branch?

Keep in mind that the program count will automatically advance to  $1A_{16}$  after the relative address is fetched from address  $19_{16}$ . Also, remember that the relative address is added to the program count. Thus, a relative address of 00 would result in a "branch" to location  $1A_{16}$ . A relative address of 01 would result in a branch to location  $1B_{16}$ . Continuing this procedure until location  $24_{16}$  is reached, you find that a relative address of  $10_{10}$  is required. That is, the relative address must be  $0A_{16}$  or  $10_{10}$ .

There is a simple procedure for determining the relative address when branching forward. Subtract the originating address from the destination address. The difference is the relative address.

In our example, the originating address is  $1A_{16}$ . Remember this is the program count at the time the relative address is added. The destination address or the address to which you wish to branch is  $24_{16}$ . Subtracting the originating address from the destination address, you find that the required relative address is

| $0010\ 0100_2$  | 2416                 | Destination address |

|-----------------|----------------------|---------------------|

| $-0001\ 1010_2$ | $1A_{16}$            | Originating address |

| 0000 10102      | $\overline{0A}_{16}$ | Relative address    |

As you can see, a relative address of  $0A_{16}$  is called for.

#### **Branching Backward**

A backward branch is used when a part of the program is to be repeated. The technique used for branching backward is similar to that used in branching forward. The difference is that a negative number is used as the relative address. As you learned earlier, two's complement representation is used to signify negative and positive numbers. Therefore, the relative address portion of any branch instruction is interpreted as a two's complement number.

This means that bit 7 of the relative address byte is a sign bit. A 0 at bit 7 tells the MPU to branch forward; a 1 tells it to branch backward. Thus, the positive values for the relative address extend from  $0000\ 0000_2$  to  $0111\ 1111_2$ . This is  $00_{16}$  to  $7F_{16}$  and  $00_{10}$  to  $+127_{10}$ .

The negative values extend from  $1111\ 1111_2$  to  $1000\ 0000_2$ . This is FF  $_{16}$  to  $80_{16}$  and -1 to  $-128_{10}$ . But remember, the relative address is with respect to the present program count. At the time the relative address is added, the program count points to the next byte after the relative address. Let's look at two examples of branching backward.

The first example is shown in Figure 4-7A. To what point does the MPU branch when the branch instruction at address  $5D_{16}$  is executed? Notice that the relative address is  $F9_{16}$ . In binary this is 1111 1001<sub>2</sub>. Recall that this is the two's complement representation of -7. Thus, the program count should jump backwards 7 bytes — but from what point? Recall that after the byte at address 5E is fetched, the program count will automatically advance to  $5F_{16}$  or 0101 1111<sub>2</sub>. When the relative address  $(F9_{16}$  or 1111 1001<sub>2</sub>) is added, the result is

The carry bit is ignored, leaving a new program count of  $58_{16}$ . Thus, the next instruction will be fetched from address  $58_{16}$ .

Figure 4-7B shows a different problem. Here we want the branch instruction at addresses B0 and B1 to direct the MPU back to address A0. What relative address is required? A simple procedure is:

- 1. Subtract the destination address from the originating address.

- 2. Take the two's complement of the difference.

|        | HEX<br>ADDRESS | HEX<br>CONTENTS | MNEMONICS/<br>HEX CONTENTS |

|--------|----------------|-----------------|----------------------------|

|        | 56             | -               | _                          |

| Progra | am 57          | -               | _                          |

| branci | hes 💉 58       | _               | _                          |

| to her | e ( 59         | <b>-</b> .      | _                          |

| 1      | 5A             | -               | _                          |

|        | 5 <b>B</b>     |                 | _                          |

|        | 5C             | _               | _                          |

|        | 5D             | 20              | BRA                        |

|        | 5E             | F9              | F9                         |

|        | 5F             |                 | <u> </u>                   |

|         | HEX<br>ADDRESS | HEX<br>CONTENTS | MNEMONICS/<br>HEX CONTENTS |

|---------|----------------|-----------------|----------------------------|

| We wish | n to A0        | _               | _                          |

| branch  |                |                 | _                          |

| here    | A2             | _               |                            |

|         | A3             | _               |                            |

|         | A4             | _               | _ :                        |

|         | A5             | -               | _                          |

|         | A6             | -               | -                          |

|         | A7             | _               | -                          |

|         | A8             | _               | _                          |

|         | A9             | _               | _                          |

|         | AA             | -               | -                          |

|         | AB             | -               | _                          |

|         | AC             | _               | _                          |

|         | AD             | -               | !                          |

|         | AE             | -               | _                          |

|         | AF             | -               | -                          |

|         | 80             | 20              | BRA                        |

|         | B1             | ??              | ??                         |

|         | B2             | -               | _                          |

В

Figure 4-7

Branching backwards.

In our example, the program count will be advanced to  $B2_{16}$  after the relative address is fetched. This is our originating address. The point to which we wish to branch is  $A0_{16}$ . This is our destination address. Subtracting yields a difference of

|   | 1011 | $0010_{2}$ | B2 <sub>16</sub> | Originating address |

|---|------|------------|------------------|---------------------|

| _ | 1010 | $0000_{2}$ | A0 <sub>16</sub> | Destination address |

|   | 0001 | 00102      | 12,6             | Difference          |

Next you compute the relative address by taking the two's complement of the difference. The two's complement of  $0001\ 0010_2$  is  $1110\ 1110_2$ . In hexadecimal this is  $EE_{16}$ . Thus, the required relative address is  $EE_{16}$ .

#### **Self-Test Review**

- 1. What addressing mode is used by the branch instruction?

- 2. What does the second byte of a branch instruction indicate?

- 3. What happens in the MPU during the execution of the branch instruction?

- 4. What type of relative address causes a branch forward?

- 5. What type of relative address causes a branch backwards?

- 6. What is the maximum number of memory locations that can be branched over during a forward branch?

- 7. What is the maximum number of memory locations that can be branched over during a backward branch?

- 8. The opcode for the branch instruction is at address 20<sub>16</sub>. The relative address is 06<sub>16</sub>. After the branch instruction is executed, from what address will the next opcode be fetched?

- 9. The opcode for the branch instruction is at address 20<sub>16</sub>. The relative address is F1<sub>16</sub>. After the branch instruction is executed, from what address will the next opcode be fetched?

#### **Answers**

- 1. Relative addressing.

- 2. The second byte of the branch instruction is the relative address. This number is added to the contents of the program counter to form the absolute address.

- The relative address is retrieved from memory and is added to the program count. The new program count goes into the program counter.

- A positive two's complement number.

- 5. A negative two's complement number.

- 6.  $0111\ 1111_2\ \text{or}\ +127_{10}$ .

- 7.  $1000\ 0000_2\ \text{or}\ -128_{10}$ .

- 8. 28<sub>16</sub>. Recall that during the execution of the branch instruction, the program counter will be incremented twice to 22<sub>16</sub>. Thus, when the relative address (06<sub>16</sub>) is added, the new address becomes 28<sub>16</sub>.

- 9. As in answer 8, the program counter is automatically advanced to  $22_{16}$  (0010 0010<sub>2</sub>) before the relative address is added. F1<sub>16</sub> is equal to 1111 0001<sub>2</sub>. When this is added to the program count, the new address becomes

Thus, the next opcode will be fetched from address 13<sub>16</sub>.

#### CONDITIONAL BRANCHING

The branch instruction allows the MPU to jump forward over a block of data or over a portion of a program. It also allows the MPU to jump backwards so a group of instructions can be repeated.

Until now we have been discussing the **unconditional** branch instruction. This type of instruction always results in a program branch. For this reason, it is called the **BR**anch Always instruction. Its mnemonic is BRA.

There are other types of branch instructions that greatly expand the versatility of the MPU. These are called **conditional** branch instructions. Unlike BRA, these instructions cause a branch only if some specified condition is met.

A good example of a conditional branch instruction is the Branch If Minus (BMI). This instruction may or may not initiate a branch operation, depending on the result of some previous arithmetic or logic operation. This instruction might be placed after a subtract instruction. If the result of the subtraction is a negative number, the branch would be implemented. Otherwise, the MPU would continue to fetch and execute instructions in numerical order. An example may help to illustrate this.

Figure 4-8 shows part of a program that uses the branch if minus (BMI) instruction. Let's start with the instruction at address  $95_{16}$ . This instruction causes the contents of location  $B0_{16}$  to be loaded into the accumulator. Next, the SUB instruction subtracts the contents of location  $B1_{16}$  from the number in the accumulator. The next instruction (BMI) examines the result of the subtraction. If the result was a minus number, the program will branch over the next three bytes. That is, the next instruction to be executed is the STA instruction at address  $9E_{16}$ . Thus, the resulting number in the accumulator is stored in location  $B3_{16}$  and the MPU halts.

If the result of the subtraction is not minus, the BMI instruction has no effect. That is, the BMI instruction is fetched and executed but no branch occurs because the specified condition is not met. In this case, the next instruction to be executed is the STA instruction at address 9B<sub>16</sub>. Thus, the result of the subtraction will be stored in location B2<sub>16</sub>.

| HEX                                                                  | HEX                                                                  | MNEMONIC/HEX                               | COMMENTS                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDRESS                                                              | CONTENTS                                                             | CONTENTS                                   |                                                                                                                                                                                                                                                      |

| 95<br>96<br>97<br>98<br>99<br>9A<br>9B<br>9C<br>9D<br>9E<br>9F<br>A0 | 96<br>B0<br>90<br>B1<br>2B<br>03<br>97<br>B2<br>3E<br>97<br>B3<br>3E | LDA B0 SUB B1 BMI 03 STA B2 HLT STA B3 HLT | Load accumulator direct with contents of this address. Subtract the contents of this address. If result is minus branch this far. If result is not minus, store at this address; then halt. If result is minus, store it at this address; then halt. |

Figure 4-8

This program uses the BMI instruction to make a simple decision.

Notice that the program flow can take one of two paths, depending on the result of the subtraction. The BMI instruction gives the MPU this capability. The conditional branch instructions are sometimes called "decision making instructions." The reason for this becomes obvious if you consider the implications of our sample program. Here the MPU decides if the number at address  $B1_{16}$  is larger than that at  $B0_{16}$ . The program path is determined by the outcome of this decision. If the number in  $B1_{16}$  is larger, the result of the subtraction is a negative number. In this case, the result is stored in location  $B3_{16}$ . Otherwise, the resulting difference is stored in location  $B2_{16}$ .

Virtually all programs must make some type of decision. Some frequently encountered decisions are:

- "Which of two numbers is larger?"

- "Does this byte represent a letter of the alphabet or a numeral?"

- "Are these two numbers equal?"

- "Is this an even number?"

- "Has the program loop been repeated the proper number of times?"

Conditional branch instructions are used in making all of these decisions.

#### **Condition Codes**

As the name implies, a conditional branch instruction causes a program branch only if some specified condition is met. Some commonly monitored conditions are:

- 1. Did a previous operation result in a negative number in the accumulator?

- 2. Did a previous operation result in zero in the accumulator?

- 3. Did a previous operation result in a carry from bit 7 of the accumulator?

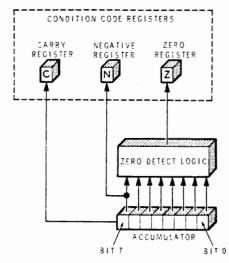

To keep track of these conditions, most microprocessors have a group of single bit registers called condition code registers. Three of these registers are shown in Figure 4-9. They are the Negative (N) Register, the Zero (Z) Register, and the Carry (C) Register.

Negative (N) Register Recall that negative numbers are expressed in two's complement form. Using this system, the most significant bit determines whether or not the number is negative. In an 8-bit byte, bit 7 is a 1 if the two's complement number is negative. Thus, the N register monitors bit 7 of the accumulator. Immediately after an operation that involves the accumulator, the N register looks at bit 7 to see if the number is negative. If so, the N register is set to 1. If the number in the accumulator is not negative, the N register is reset to 0.

Most operations that involve the accumulator affect the N register in this way — **but not all**. In a later unit we will point out how this register is affected by each instruction. In this unit, we will assume that the N register is affected as outlined above any time a number is added to, subtracted from, loaded into, or stored from the accumulator.

Another name for a condition code is a flag. Thus, the N register is sometimes called the N flag or the negative flag.

**Zero (Z) Register** This register monitors the accumulator looking for all zeros. Immediately after an operation that involves the accumulator, the zero-detect circuit looks at the resulting number. If all 8 bits are 0, the Z register is set to 1. Otherwise, the Z register is reset to 0. Most operations that involve the accumulator affect the Z register in this way.

Figure 4-9

Condition code registers monitor the operations in the accumulator.

Carry (C) Register The C register acts somewhat like an extension of the accumulator. You have seen that when two unsigned 8-bit numbers are added, the sum is frequently a 9-bit number. For example:

Since the accumulator is an 8-bit register, the sum will not fit. The most significant bit (the carry) would be lost if you did not have another 1-bit register to hold it. This is the purpose of the C register. Any operation that causes a carry out of bit 7 will set the carry register to 1. Arithmetic operations that do not result in a carry will reset this register to 0.

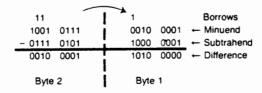

The carry register is also used to keep track of "borrows" during subtract operations. If a subtraction requires a borrow for bit 7, the carry flag will also be set. For example, suppose you subtract an unsigned, binary number from a smaller unsigned binary number. The result will, of course, be a negative number. Moreover, bit 7 will have to "borrow" a bit to complete the subtraction. As a simple example, let's subtract 2 from 1. The subtraction looks like this

The carry bit is set to 1 to indicate that a borrow operation occurred. Many subtraction operations do not require borrows. In these cases, the carry bit is reset to 0 to indicate that no borrow occurred.

Notice that the carry code can have different meanings, depending on the operation involved. That is, a 1 can mean either that a carry occurred or that a borrow occurred. The precise meaning of the 1 depends on whether the operation was an addition or a subtraction. We will discuss some additional aspects of the carry register in a later unit.

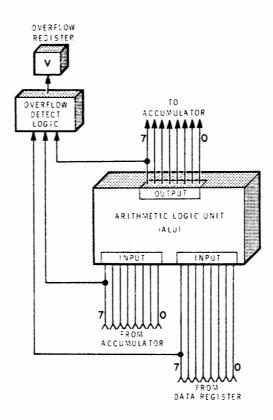

Overflow (V) Register The final condition code that is to be considered in this unit keeps track of two's complement overflow. Figure 4-10 shows how this register is connected in the MPU. A special circuit detects an overflow condition by monitoring bit 7 of the ALU's input and output lines. This circuit sets the V flag when an overflow occurs but clears it if no overflow occurs.

Figure 4-10 The overflow register monitors bit 7 of the ALU's input and output lines.

Let's see what is meant by two's complement overflow. Recall that the ALU adds numbers as if they were unsigned binary numbers. Even so, it can handle signed binary numbers if the proper bit patterns represent the negative numbers. This is the reason that the two's complement method of representing signed numbers has become so popular. A disadvantage of this system is that the magnitude of the number must be represented by 7 bits, since the eighth bit is used as the sign. Remember that a 1 in the MSB defines the number as negative.

Unfortunately, if two signed numbers are added and their sum exceeds 7-bits, the sign bit will be changed. For example, assume that a program adds  $+73_{10}$  and  $+96_{10}$ . The addition looks like this:

$$\begin{array}{c|cccc} \underline{0100} & 1001_2 & +73_{10} \\ \underline{0110} & 0000_2 & +96_{10} \\ \hline \underline{1010} & 1001_2 & 169_{10} \end{array}$$

The answer is correct if all the binary numbers represent unsigned quantities. However, using two's complement, the underlined bits represent sign bits. Therefore, the answer does **not** represent  $169_{10}$ . Instead, it represents  $-87_{10}$ . The reason for this error is that there was an overflow from bit 6 into the sign bit (bit 7). This is one of the situations that the V flag indicates.

When two's complement numbers having the same sign are added, the sum should have the same sign. That is, when two positive numbers are added, the sum should be positive. By the same token, when two negative numbers are added, the sum should be negative. However, an overflow can cause the sign to be reversed. The overflow logic detects this situation and sets the V flag whenever an overflow occurs.

The sign bit can also be upset during subtract operations. For example, when a negative number is subtracted from a positive number, the results should be positive. Remember that subtracting a negative number is tantamount to adding a positive number. However, in certain cases, an overflow can reverse the sign bit. This type of overflow occurs when the signs of the minuend and subtrahend are opposite and the difference has the sign of the subtrahend. This condition also sets the V flag.

#### **Conditional Branch Instructions**

The conditional branch instructions available in our hypothetical microprocessor are shown in Figure 4-11. While these are largely selfexplanatory, a couple of points should be mentioned.

| INSTRUCTION              | MNEMONIC | OPCODE | BRANCH IF |

|--------------------------|----------|--------|-----------|

| Branch If Carry Clear    | всс      | 24     | C=0       |

| Branch If Carry Set      | BCS      | 25     | C=1       |

| Branch If Not Equal Zero | BNE      | 26     | Z=0       |

| Branch If Equal Zero     | BEQ      | 27     | Z=1       |

| Branch if Plus           | BPL      | 2A     | N=0       |

| Branch If Minus          | ВМІ      | 2B     | N=1       |

| Branch If Overflow Clear | вус      | 28     | V=0       |

| Branch If Overflow Set   | BVS      | 29     | V=1       |

Figure 4-11 Conditional Branch Instructions.

The first instruction, Branch If Carry Clear (BCC), monitors the C register. If the carry register is reset to 0, the branch is implemented. Notice that the words "clear" and "reset" are used interchangeably in this regard. They both mean the register contains a 0.

The branch instructions that monitor the Z register can also be confusing. The Branch If Equal Zero (BEQ) instruction implements a branch when the Z register is set to 1. Recall that the Z register is set to 1 when the number in the accumulator is zero. Thus, you must remember that a 0 in the Z register means that the number in the accumulator is **not** zero.

These conditional branch instructions can be used with other instructions to make a wide range of decisions. They greatly increase the power of the microprocessor. More than any other type of instruction, the conditional branches are responsible for the MPU's "intelligence." In the next section, you will see how these instructions are used.

#### **Self-Test Review**

- 10. What is the difference between an unconditional branch instruction and a conditional branch instruction?

- 11. What condition is tested by the branch if minus (BMI) instruction?

- 12. When is the N flag set?

- 13. When is the Z flag set?

- 14. During an add operation, the C flag is set. What does this represent?

- 15. During a subtract operation, the C flag is set. What does this indicate?

- 16. Often, when two positive 2's complement numbers are added, the sign bit of the answer will indicate a negative sum. This "error" can be spotted by checking which flag?

- 17. Under what condition will the BEQ instruction cause a branch to occur?

- 18. Under what condition will the BPL instruction cause a branch to occur?

- 19. When subtracting unsigned binary numbers, which flag indicates that the difference is a negative number?

#### **Answers**

- An unconditional branch instruction always causes a branch operation to occur. On the other hand, the conditional branch instruction implements a branch operation only if some specified condition is met.

- 11. The BMI instruction tests the Negative (N) register to see if it is set.

- 12. Generally speaking, the N flag is set if the previous instruction left a 1 in the MSB of the accumulator.

- 13. Generally, the Z flag is set if the previous instruction left all zeros in the accumulator.

- 14. During an add operation, the carry bit is set if there is a carry from bit 7 of the accumulator.

- 15. During a subtract operation, the carry bit is set if bit 7 had to "borrow" a bit to complete the subtraction.

- 16. This condition results from a two's complement overflow. Thus, the V flag will be set if this condition occurs.

- 17. The BEQ instruction causes a branch to occur only if the Z register is set.

- 18. The BPL instruction causes a branch to occur only if the N register is clear.

- 19. The carry flag.

#### **ALGORITHMS**

An algorithm is a step-by-step procedure for doing a particular job. It generally involves doing a complex task by stringing together a series of simple steps. To illustrate the use of an algorithm, consider the following very simple example.

#### Multiplying by Repeated Addition

Most microprocessors do not have hardware multiply capabilities. That is, they do not have a multiplication circuit nor a multiply instruction. Nevertheless, the microprocessor can be made to multiply by use of an algorithm. One procedure for doing this was discussed earlier. It involved adding the multiplicand to itself the number of times indicated by the multiplier. In the previous example, this was done by using a separate ADD instruction for each addition. This procedure is unsatisfactory for two reasons. First, it results in excessively long programs. Second, you must know the value of the multiplier so that you know how many ADD instructions to include.

A better approach, although still far from ideal, is to use a program loop that will multiply two numbers by repeated addition. For the time being, assume that the two numbers are both positive and that the product does not exceed 255<sub>10</sub>. Let's further assume that we use only the instructions which have been discussed up to this point. In fact, we will restrict ourselves to the instructions shown in Figure 4-12.

|                       | MNEMONIC | ADDRESSING MODE |            |          |          |

|-----------------------|----------|-----------------|------------|----------|----------|

| INSTRUCTION           |          | IMMEDIATE       | DIRECT     | RELATIVE | INHERENT |

| Load Accumulator      | LDA      | 86              | 96         |          |          |

| Clear Accumulator     | CLRA     |                 |            |          | 4F       |

| Decrement Accumulator | DECA     |                 |            |          | 4A       |

| Increment Accumulator | INCA     |                 |            |          | 4C       |

| Store Accumulator     | STA      |                 | 97         |          |          |

| Add                   | ADD      | 88              | 9 <b>B</b> |          |          |

| Subtract              | SUB      | 80              | 90         |          |          |

| Branch Always         | BRA      |                 |            | 20       |          |

| Branch If Carry Set   | BCS      |                 |            | 25       |          |

| Branch if             | BEQ      |                 |            | 27       |          |

| Equal Zero            |          |                 | }          |          | L        |

| Branch if Minus       | ВМІ      |                 |            | 2B       |          |

| Halt                  | HLT      |                 |            |          | 3E       |

Figure 4-12 Instructions to be used.

The algorithm for multiplying by repeated addition is quite simple. To multiply A times B, you merely add A to a specific location B times. For example, to multiply 5 times 3, you clear a location and then add 5. You continue the addition until 5 has been added 3 times. The number in the affected location will then be  $15_{10}$  which is the product of 5 times 3.

The success of this operation depends on the microprocessor knowing when to stop. It must add 5 three times, but only three times. One way to keep track of the number of additions is to decrement the multiplier (3) each time an addition is made. When the multiplier reaches 0, the proper number of multiplications has been carried out.

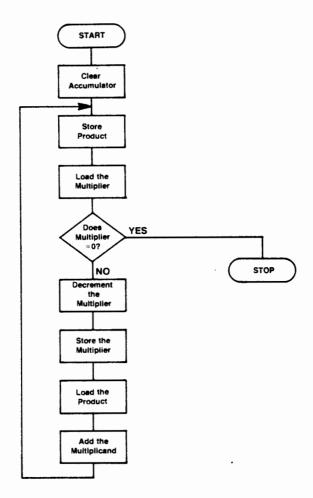

Figure 4-13 is a flow chart that illustrates the algorithm. In the first two steps, the MPU clears the accumulator and stores the resulting number (0) in the product. This ensures that the product is zero before the first number is added. Next, it loads the multiplier and checks to see if the multiplier is 0. If so, the process is stopped since a multiplier of 0 dictates a product of 0.

In our example, the multiplier is 3; therefore, we exit the decision block via the "no" line. The next step tells us to decrement the multiplier. The new value of the multiplier (2) is stored for future use. Next, the product whose present value is 0 is loaded. Then, the multiplicand (5) is added so that the new value of the product becomes 5. This completes our first pass through the program. Remember that the multiplicand has been added once and that the multiplier has been reduced by one.

Notice that the program loops back to the input of the second block. The product which now has a value of 5 is stored back in memory. The multiplier (which is now 2) is loaded and tested. Because its value is not yet 0, the multiplier is decremented to 1 and stored again. The product (whose value is now 5) is then loaded and the multiplicand is added so that a new value of  $10_{10}$  is obtained.

The program loops again and the new product  $(10_{10})$  is stored. The multiplier (whose value is now 1) is loaded and tested. Because its value is still not 0, it is decremented again. Notice that the value of the multiplier is now 0. This value is stored away, the product  $(10_{10})$  is fetched, and the multiplicand is added once more. The new value of the product becomes  $15_{10}$ .

Figure 4-13

Flow chart for multiplying by repeated addition.

The program loops again and the product is stored. The multiplier is loaded and tested. Recall that the value of the multiplier is now 0. Consequently, we exit the decision block via the "yes" line. The program has accomplished its task and it now stops. Notice that the value of the product is  $15_{10}$  which is the proper answer for  $5\times3$ .

The next task is to convert the flow chart to a program that the computer can execute. Figure 4-14 shows such a program. Carefully compare this program to the flow chart paying particular attention to the comments column. Work through the program on paper and verify that it will multiply the numbers at addresses  $11_{16}$  and  $12_{16}$ . Although 3 and 5 are used in this example, the program will work for any values of multiplier and multiplicand as long as the product does not exceed  $255_{10}$ .

| HEX                                                                                                      | HEX                                                                                                            | MNEMONIC/HEX                                                         | COMMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDRESS                                                                                                  | CONTENTS                                                                                                       | CONTENTS                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 00<br>01<br>02<br>03<br>04<br>05<br>06<br>07<br>08<br>09<br>0A<br>0B<br>0C<br>0D<br>0E<br>0F<br>10<br>11 | 4F<br>97<br>13<br>96<br>12<br>27<br>09<br>4A<br>97<br>12<br>96<br>13<br>9B<br>11<br>20<br>F1<br>3E<br>05<br>03 | CLRA STA 13 LDA 12 BEQ 09 DECA STA 12 LDA 13 ADD 11 BRA F1 HIT 05 03 | Clear the accumulator.  Store the product in location 13 <sub>16</sub> .  Load the accumulator with the multiplier from location 12 <sub>16</sub> If the multiplier is equal to zero, branch down to the Halt instruction. Otherwise, decrement the multiplier. Store the new value of the multiplier back in location 12 <sub>16</sub> .  Load the accumulator with the product from location 13 <sub>16</sub> .  Add the multiplicand to the product. Branch back to instruction in location 01.  Halt.  Multiplicand.  Multiplier.  Product. |

Figure 4-14

This program multiplies the numbers at addresses 11<sub>16</sub> and 12<sub>18</sub>, and places their product at address 13<sub>16</sub>.

#### **Dividing by Repeated Subtraction**

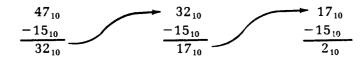

Another interesting algorithm is one that allows the microprocessor to divide by repeated subtraction. The technique is to keep track of the number of times that the divisor can be subtracted from the dividend. For example, suppose you wish to divide  $47_{10}$  by  $15_{10}$ . The divisor can be subtracted 3 times:

First subtraction Second Subtraction Third Subtraction

Because three subtractions occurred, the quotient is 3. Also, because 2 was left after the last subtraction, the remainder is 2. We can verify this by long division:

divisor

$$\rightarrow$$

15<sub>10</sub>  $\rightarrow$  15<sub>10</sub>  $\leftarrow$  Quotient  $\rightarrow$  Dividend  $\rightarrow$  45<sub>10</sub>  $\leftarrow$  Remainder

The microprocessor keeps track of the number of subtractions by incrementing the quotient by one each time a subtraction occurs. Of course, the quotient must be initially set to zero.

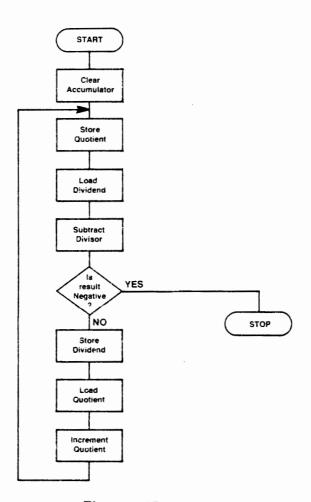

The divisor is subtracted from the dividend until any further subtraction would result in a negative number. The MPU can use the BMI instruction to check for a negative result on each loop. The negative result is the indication that the process is finished.

A flow chart for this algorithm is shown in Figure 4-15. The actual program is shown in Figure 4-16. The program is arbitrarily placed in locations 00 through  $10_{16}$ . The dividend  $(47_{10})$  is at address  $11_{16}$  while the divisor  $(15_{10})$  is at address  $12_{16}$ . When executed, the program will produce the quotient at location  $13_{16}$  and the remainder at location  $11_{16}$ .

Flow chart for dividing by repeated subtraction.

| HEX<br>ADDRESS                                                                                     | HEX<br>CONTENTS                                                                                              | MNEMONIC/HEX CONTENTS                                       | COMMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00<br>01<br>02<br>03<br>04<br>05<br>06<br>07<br>08<br>09<br>0A<br>0B<br>0C<br>0D<br>0E<br>0F<br>10 | 4F<br>97<br>13<br>96<br>11<br>90<br>12<br>28<br>07<br>97<br>11<br><br>96<br>13<br>4C<br>20<br>F1<br>3E<br>2F | CLRA STA 13 LDA 11 SUB 12 BMI -07 STA 11 LDA 13 INCA BRA F1 | Clear the accumulator.  Store in the quotient which is at address location 13 <sub>16</sub> .  Load the accumulator with the dividend from location 11 <sub>16</sub> .  Subtract the dividend. If the difference is negative, branch down to the Halt instruction.  Otherwise, store the difference back in location 11 <sub>16</sub> .  Load the accumulator with the quotient. Increment the quotient by one. Branch back to instruction in location 01.  Halt.  Dividend (47 <sub>16</sub> ).  Divisor (15 <sub>16</sub> ). |

| 13                                                                                                 | _                                                                                                            | _                                                           | Quotient.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Figure 4-16

This program divides by repeatedly subtracting the divisor from the dividend.

Refer to the flow chart and the comments column of the program. Before reading further, try running through the program on paper. This will give you a feel for how the computer solves the problem.

Now let's go through the program to see what it does. The first two instructions clear the quotient. Next, the dividend ( $47_{10}$ ) is loaded into the accumulator and the divisor ( $15_{10}$ ) is subtracted. The BMI instruction is used to examine the difference ( $32_{10}$ ). Since the difference is not minus, the branch does not occur. Consequently, the next instruction stores the difference ( $32_{10}$ ) back in the location from which the dividend came. In effect, the difference becomes the new dividend. Next the quotient (0) is loaded and is incremented to 1. The program then branches back to the instruction in location 01. This instruction stores the quotient (1) back in location  $13_{16}$ .

On the next pass through the program, the new dividend ( $32_{10}$ ) is loaded and the divisor ( $15_{10}$ ) is subtracted again. This produces a difference of ( $17_{10}$ ). Since the difference is not negative, the BMI instruction does not cause a branch. Thus, the difference is stored back in location  $11_{16}$ . The quotient is loaded into the accumulator and is incremented to 2. The BRA instruction causes the program to loop once again. The STA instruction in location 01 stores the quotient (2) back in location  $13_{16}$ .

On the third pass the dividend  $(17_{10})$  is loaded and the divisor  $(15_{10})$  is subtracted a third time. The difference (02) is still not negative so no branch occurs. The difference is stored away; the quotient is loaded and is incremented to 03. Notice that this is the proper final value for the quotient. Therefore, on the next pass, the MPU should be able to break out of the loop.

The quotient is stored back in location  $13_{16}$ . The dividend, which now has a value of 2, is loaded. The divisor  $(15_{10})$  is subtracted, leaving a negative number  $(-13_{10})$  in the accumulator. The BMI instruction recognizes that this is a negative number and implements a branch operation. Notice that the MPU branches forward to the HLT instruction. Thus, the program ends with the quotient set to 3. The remainder is at address  $11_{16}$ . That is, the remainder is what remains of the dividend after the third subtraction.

It may bother you that there were four subtractions and that a negative difference resulted from the last subtraction. However, you will recall that the quotient was incremented only on the first three of these subtractions. Thus, the final quotient is 3. Moreover, the negative difference that resulted during the last subtraction was never stored. Consequently, the remainder was 2 when the program ended.

This program does have some drawbacks. For one thing, neither the dividend nor the divisor can exceed 127<sub>10</sub>. Also, only positive numbers can be used. Finally, the program gets hung up in an endless loop if the initial value of the divisor is zero. While division by zero is not allowed in mathematics, some provision would be made in a practical program to recognize this eventuality. Since the program is for demonstration purposes, we will live with these shortcomings for the time being.

## **Converting BCD to Binary**

When a microprocessor is used with a terminal such as a teletypewriter, numerals are entered as ASCII characters. For example, the number  $237_{10}$  is entered into memory as three ASCII characters:

| Numeral | ASCII C | ASCII Character |  |  |

|---------|---------|-----------------|--|--|

| 2       | 0011    | 0010            |  |  |

| 3       | 0011    | 0011            |  |  |

| 7       | 0011    | 0111            |  |  |

Notice that the four least significant bits of the ASCII character represent the BCD value of the corresponding numeral. Thus, we can convert these ASCII characters to BCD numbers simply by eliminating the four most significant bits. This technique was demonstrated in an earlier experiment.

While the microprocessor does have some BCD capability, it is often desirable to convert BCD numbers to binary. The technique for doing this illustrates another useful algorithm.

The BCD representation for 237<sub>10</sub> is:

0010 ← hundreds BCD digit 0011 ← tens BCD digit 0111 ← units BCD digit

Notice that in this example 0010 represents two hundred, 0011 represents thirty, and 0111 represents seven. Because of this, there is a simple procedure for converting BCD to binary. Starting with an initial value of zero, the MPU adds  $100_{10}$  as many times as indicated by the hundreds digit. It then adds  $10_{10}$  as indicated by the tens digit. Finally, the value of the units digit is added on to the result. The steps involved look like this:

| $1100100_2$ | 10010               | One hundred added     |

|-------------|---------------------|-----------------------|

| $1100100_2$ | 10010               | 2 times               |

| $1010_2$    | 1010                | Ì                     |

| $1010_{2}$  | 1010                | Ten added three times |

| $1010_2$    | 1010                | )                     |

| 01112       | 710                 | 7 units added         |

| 111011012   | = 237 <sub>10</sub> |                       |

As you can see, this procedure ends with a binary result of 1110  $\,$  1101, which is the binary representation for 237<sub>10</sub>.

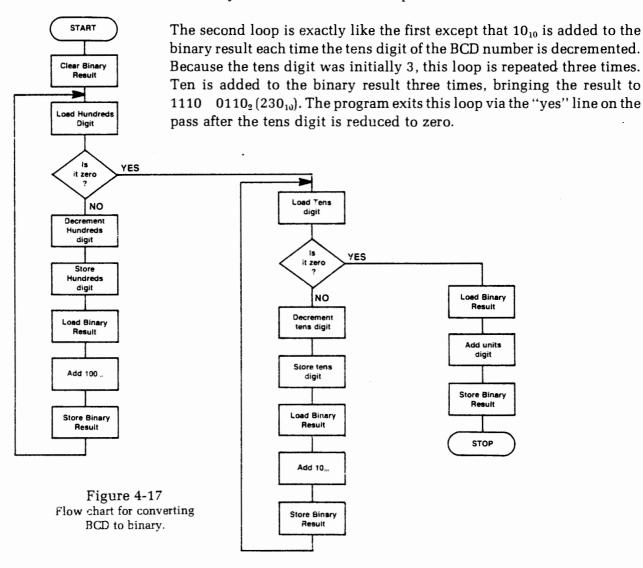

A flow chart for this procedure is shown in Figure 4-17. Here, the first step is to clear the binary result. We will be adding to this result, so it must start out at zero.

Next the program enters a loop in which it adds  $100_{10}$  to the binary result the number of times indicated by the hundreds digit of the BCD number. The hundreds digit is loaded and tested for zero. If it is not zero, the hundreds digit is decremented and stored back in memory. Then the binary result is loaded and  $100_{10}$  is added. The result is stored away and the loop is repeated. In our example, the hundreds digit was initially 2. Thus, this loop is repeated twice. The binary result will have the value  $1100 \quad 1000_2 \ (200_{10})$  when the hundreds digit is reduced to zero. At that time, the program exits the decision block via the "yes" line and immediately encounters a second loop.

The final three blocks add the units digit to the binary result. In our example, the units digit was  $7_{10}$ . This brings the final binary result to  $1110 \quad 1101_2$ . Notice that this is the proper binary representation for the unsigned number  $237_{10}$ .

A program that carries out this operation is shown in Figure 4-18. The three digit BCD number is stored in locations  $28_{16}$ ,  $29_{16}$ , and  $2A_{16}$ . The binary equivalent will be computed and placed in location  $2B_{16}$ . Before reading further, try to work through the program. Refer to the flow chart and the comments column as you trace out the sequence that the MPU will follow.

| · HEX<br>ADDRESS | HEX<br>CONTENTS | MNEMONIC/HEX CONTENTS                     | COMMENTS                                       |

|------------------|-----------------|-------------------------------------------|------------------------------------------------|

| 00               | 4F              | CLRA                                      | Clear the accumulator.                         |

| 01               | 97              | STA                                       | Store 00                                       |

| 02               | 2 <b>B</b>      | . 2B                                      | in location 2B. This clears the binary result. |

| 03               | 96              | Significa <del>tion</del> LDA Parabasisis | Load direct                                    |

| 04               | 2 <b>8</b>      | 28                                        | the hundreds BCD digit.                        |

| 05               | 27              | BEQ                                       | If the hundreds digit is zero, branch          |

| 06               | 0B              | DO DO DE COMPANS                          | forward to the instruction in location 12,     |

| 07               | 4A              | DECA                                      | Otherwise, decrement the accumulator.          |

| 08               | 97              | STA CONTROL                               | Store the result as the new                    |

| 09               | 28              | 28                                        | hundreds BCD digit.                            |

| 0A               | 96              | LDA                                       | Load direct                                    |

| 0B               | 2 <b>B</b>      | 2 <b>B</b>                                | the binary result.                             |

| OC               | 8B              | ADD                                       | Add immediate                                  |

| 0D               | 64              | 64 (666)                                  | 100 to the binary result.                      |

| 0E               | 97              | STA                                       | Store away the new                             |

| 0F               | 2 <b>B</b>      | 2B                                        | binary result.                                 |

| 10               | 20              | BRA                                       | Branch                                         |

| 11               | F1              | F1 (000000000000000000000000000000000000  | back to the instruction in location 03         |

| 12               | 96              | LDA                                       | Load direct                                    |

| 13               | 29              | 29                                        | the tens BCD digit.                            |

| 14               | 27              | —/—BEQ                                    | If the tens BCD digit is zero, branch          |

| 15               | 0B              | ОВ                                        | forward to the instruction in location 21,,    |

| 16               | 4A              | DECA                                      | Otherwise, decrement the accumulator.          |

| 17               | 97              | STA                                       | Store the result as the new                    |

| 18               | 29              | 29                                        | tens BCD digit.                                |

| 19               | 96              | LDA                                       | Load direct                                    |

| 1A               | 2B              | 2B                                        | the binary result.                             |

| 18               | 8B              | ADD                                       | Add immediate                                  |

| 1C               | 0A              | OA.                                       | 10,, to the binary result.                     |

| 1D               | 97              | STA                                       | Store away the new                             |

| 1E               | 2B              | 2B                                        | binary result.                                 |

| 1F               | 20              | BRA                                       | Branch                                         |

| 20               | F1              | F1                                        | back to the instruction in location 12 in-     |

| 21               | 96              | LDA                                       | Load direct                                    |

| 22               | 2B              | 2B                                        | the binary result.                             |

| 23               | 9B              | ADD                                       | Add direct                                     |

| 24               | 2 <b>A</b>      | 2A                                        | the units BCD digit.                           |

| 25               | 97              | STA                                       | Store away the new                             |

| 26               | 2B              | 2B                                        | binary result.                                 |

| 27               | 3E              | HLT SEEDS                                 | Halt.                                          |

| 28               | 02              | 02                                        | Hundreds BCD digit.                            |

| 29               | 03              | 03                                        | Tens BCD digit.                                |

| 2A               | 07              | 07                                        | Unit BCD digit.                                |

| 2B               |                 | _                                         | Reserved for the binary result.                |

Figure 4-18

Program for converting BCD to binary.

Now let's briefly go through the program. The first two instructions clear the location at which the binary number will be formed.

Next, the program enters the first loop, which is shown as the first shaded area. In this loop, the hundreds digit is loaded and tested for zero. If not zero, it is decremented and stored away. Then the binary result is loaded and  $100_{10}$  is added. The result is stored away and the loop is repeated. Because the hundreds digit was 02 initially,  $100_{10}$  will be added to the binary result twice. Thus, upon leaving this loop, the binary result will have the value  $200_{10}$ . The MPU escapes this loop when the BEQ instruction at address 05 detects that the hundreds digit has been reduced to zero. The branch is to the second loop which is shown as an unshaded area.

In the second loop, the tens digit is loaded and tested for zero. If not zero, it is decremented and stored away. Then the binary number is loaded,  $10_{10}$  is added, and the result is stored away. This loop is repeated until the tens digit is reduced to zero. Because the tens digit was initially three, the loop is repeated three times so that thirty is added to the binary number. The BEQ instruction at address  $14_{16}$  allows the MPU to escape the loop and branch to the final program segment.

This final segment is the last shaded area. Here, the binary result is loaded and the units digit is added. This brings the binary result to 237<sub>10</sub>. Then the result is stored and the program halts. While the number 237<sub>10</sub> was used in this example, the program will convert any BCD number between 000 and 255<sub>10</sub> to its binary equivalent.

### **Converting Binary to BCD**

A microprocessor generally manipulates data in the form of straight binary numbers. However, before the results can be transmitted to the outside world, the data is often converted back to BCD. Frequently, this is an intermediate step in converting back to ASCII.

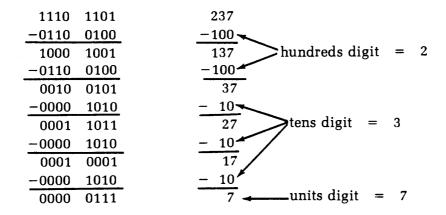

The binary-to-BCD conversion is the reverse of the process that occurred in the previous program. The MPU must determine how many times  $100_{10}$  can be subtracted from the binary number. The answer becomes the hundreds BCD digit. After the  $100_{10}$  has been subtracted as many times as possible,  $10_{10}$  is subtracted repeatedly from the remaining number. The number of subtractions becomes the tens BCD digit. Finally, after  $10_{10}$  has been subtracted as many times as possible, the remaining number becomes the units BCD digit.

For the number 1110  $1101_2$  (237<sub>10</sub>), the process looks likes this:

One hundred can be subtracted twice. Thus, the hundreds digit is  $2_{10}$  or  $0010_2$ . From the remainder, ten can be subtracted three times. Thus, the tens digit is  $3_{10}$  or  $0011_2$ . Finally, the remainder of  $7_{10}$  or  $0111_2$  becomes the units digit. The BCD representation is  $0010 \quad 0011 \quad 0111$ .

Start

Cles

Hundreds Digit

Clear

Units Digit

Load Sinan

Numbe

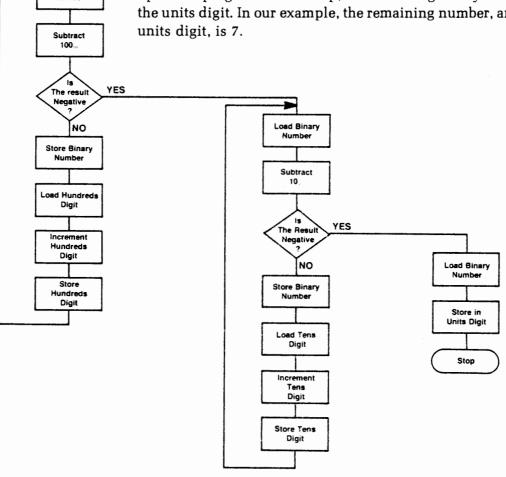

Figure 4-19 shows the flow chart for this procedure. The first three blocks clear the hundreds, tens, and units digits of the BCD result. Then the binary number that is to be converted to BCD is loaded and  $100_{10}$  is subtracted. The outcome is tested to see if a negative number resulted. If not, the result is stored away. The hundreds digit is loaded, incremented, and stored away. The loop is repeated until  $100_{10}$  can no longer be subtracted. In our example,  $100_{10}$  can be subtracted twice. Therefore, the hundreds digit is incremented to 2. The third subtraction of  $100_{10}$  gives a negative result. This allows the MPU to escape the first loop.

The second loop increments the tens digit to the proper value by subtracting  $10_{10}$  repeatedly and keeping track of the number of subtractions. In our example, this loop is repeated three times. Consequently, the tens digit is incremented to 3. The binary number that is left over after  $10_{10}$  is subtracted the proper number of times becomes the units digit. That is, upon escaping the second loop, the remaining binary number is stored in the units digit. In our example, the remaining number, and therefore the units digit, is 7.

Flow chart for converting a binary number to a BCD number.

The program that carries out this procedure is shown in Figure 4-20. At this point, you should be able to interpret the program from the comments given. However, a couple of points should be explained briefly. Any unsigned binary number from 0000 0000 to 1111 1111 can be placed at address  $2A_{16}$ . The computer will convert this number into its BCD equivalent. The hundreds digit will appear at address  $2B_{16}$ , the tens digit at  $2C_{16}$ , and the units digit at  $2D_{16}$ . The decision making instructions at addresses  $0B_{16}$  and  $1A_{16}$  are Branch if Carry Set (BCS) instructions. Because these instructions follow immediately after SUB instructions, the carry flag will indicate whether or not a borrow occurred. In effect, the BCS instructions decide: "Was the result of the subtraction a negative number?"

| HEX<br>ADDRESS | HEX<br>CONTENTS | MNEMONIC/HEX<br>CONTENTS | COMMENTS                                                       |  |

|----------------|-----------------|--------------------------|----------------------------------------------------------------|--|

| 00             | 4F              | CLRA                     | Clear the accumulator.                                         |  |

| 01             | 97              | STA                      | Store 00                                                       |  |

| 02             | 2 <b>B</b>      | 2B                       | in location 2B <sub>16</sub> . This clears the hundreds digit. |  |

| 03             | 97              | STA                      | Store 00                                                       |  |

| 04             | 2C              | 2C                       | in location 2C <sub>16</sub> . This clears the tens digit.     |  |

| 05             | 97              | STA                      | Store 00                                                       |  |

| 06             | 2D              | 2D                       | in location 2D <sub>16</sub> . This clears the units digit.    |  |

| 07             | 96              | LDA                      | Load direct                                                    |  |

| 08             | 2 <b>A</b>      | 2A                       | the binary number to be converted.                             |  |

| 09             | 80              | SUB                      | Subtract immediate                                             |  |

| 0 <b>A</b>     | 64              | 64                       | 100                                                            |  |

| 0B             | 25              | BCS                      | If a borrow occurred, branch                                   |  |

| 0C             | 09              | 09                       | forward to the instruction in location 16 <sub>16</sub> .      |  |

| 0 <b>D</b>     | 97              | STA                      | Otherwise, store the result of the subtraction                 |  |

| 0 <b>E</b>     | 2 <b>A</b>      | 2 <b>A</b>               | as the new binary number.                                      |  |

| 0F             | 96              | LDA                      | Load direct                                                    |  |

| 10             | 2 <b>B</b>      | 28                       | the hundreds digit of the BCD result.                          |  |

| 11             | 4C              | INCA                     | Increment the hundreds digit.                                  |  |

| 12             | 97              | STA                      | Store the hundreds digit                                       |  |

| 13             | 2 <b>B</b>      | 2 <b>B</b>               | back where it came from.                                       |  |

| 14             | 20              | BRA                      | Branch                                                         |  |

| 15             | F1              | F1 '                     | back to the instruction at address 0716                        |  |

| 16             | 96              | LDA                      | Load girect                                                    |  |

| 17             | 2A              | 2 <b>A</b>               | the binary number.                                             |  |

| 18             | 80              | SUB                      | Subtract immediate                                             |  |

| 19             | 0 <b>A</b>      | 0 <b>A</b>               | 10,0.                                                          |  |

| 1A             | 25              | BCS                      | If a borrow occurred, branch                                   |  |

| 1B             | 09              | 09                       | forward to the instruction in location 25 <sub>18</sub> .      |  |

| 1C             | 97              | STA                      | Otherwise, store the result of the subtraction                 |  |

| 1D             | 2A              | 2A                       | as the new binary number.                                      |  |

| 1E             | 96              | LDA                      | Load direct                                                    |  |

| 1F             | 2C              | 2C                       | the tens digit.                                                |  |

| 20             | 4C              | INCA                     | Increment the tens digit.                                      |  |

| 21             | 97              | STA                      | Store the tens digit                                           |  |

| 22             | 2C              | 2 <b>C</b>               | back where it came from.                                       |  |

| 23             | 20              | BRA                      | Branch                                                         |  |

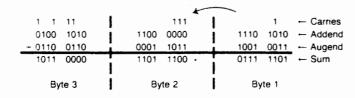

| 24             | F1              | F1                       | back to the instruction at address 16 <sub>16</sub> .          |  |